基于ARM和FPGA的高速图像数据采集板设计

32位微处理器连接,并且可以像SRAM一样被访问;它有40KBytesSRAM网络封包缓存器。它符合IEEE802.3/IEEE802.3u/IEEE802.3ab协议,可广泛应用于各种消费电子和家庭网络市场或要求更高的网络带宽连接,如数字媒体、家用网关及IP电视等。

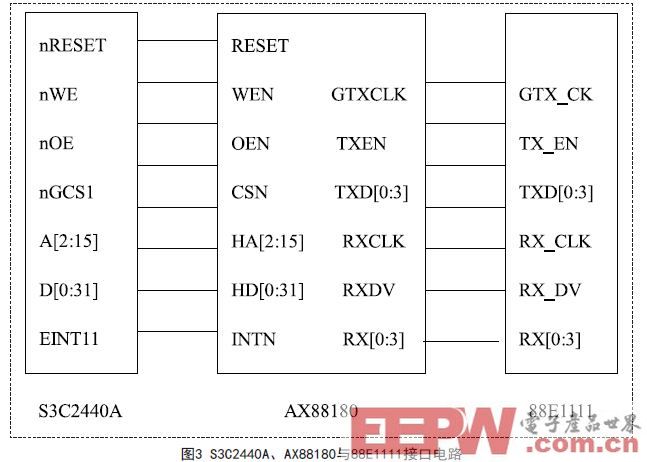

嵌入式芯片S3C2440A、以太网控制器AX88180及物理层芯片88E1111的接口电路图如图3所示。

?

?

S3C2440A与AX88180之间采用总线方式相连,地址总线A2~A15、数据总线D0~D31、读写信号等可以直接连接,AX88180中断信号与S3C2440A EINT11相连,AX88180的40M~100M时钟信号由S3C2440A提供,整个接口电路无需外加电路;AX88180与PHY芯片之间采用简化千兆比特媒体RGMII接口,信号对应 相连,负责实现数据传送底层协议[5].

3.Linux驱动程序设计

FPGA作为ARM的外设,需要设计它在Linux下的驱动程序。驱动程序是操作系统与硬件之间的接口,它为应用程序屏蔽硬件的细节。硬件系统只有和高效可靠的驱动程序相结合才能在操作系统下正常工作。

Linux的设备驱动程序需要完成如下功能:

①对设备进行初始化和释放。

②提供各类设备服务。

③负责内核和设备之间的数据交换。

④检测和处理设备工作过程中出现的错误。

Linux下的设备驱动程序被组织成一组完成不同任务的函数集合,通过这些函数使Windows的设备操作犹如文件一般。

Linux将设备分为字符设备和块设备两类。我们使用的是字符设备。驱动程序的模块化我们先不做介绍,我们主要介绍Linux下的中断[6].Linux将中断处理程序分解成两个半部:上半部和下半部。上半部完成尽可能少的比较紧急的功能,下半部用来完成中断事件的绝大部分任务。因为中断的耗时工作在这里完成,所以将读取数据放在下半部完成。Linux系统实现下半部采用的机制主要有tasklet、工作队列和软中断。许多设备涉及到中断操作,因此,在这样的设备的驱动程序中需要对硬件产生的中断请求提供中断服务程序。与注册基本入口点一样,驱动程序也要请求内核将特定的中断请求和中断服务程序联系在一起。在Linux中,用request_irq()函数来实现请求:

int request_irq(unsigned intirq,void(*handler)int,unsigned longtype,char*name);

参数irq为要中断请求号,参数handler为指向中断服务程序的指针,参数type用来确定是正常中断还是快速中断(正常中断指中断服务子程序返回后,内核可以执行调度程序来确定将运行哪一个进程;而快速中断是指中断服务子程序返回后,立即执行被中断程序,正常中断type取值为0,快速中断type取值为SA_INTERRUPT),参数name是设备驱动程序的名称。

我们的中断处理函数是:

void fpgalc12_interrupt(int irq,void*dev_id,struct pt_regs*regs)。

Irqflags是中断处理的属性,若设置了SA_INTERRUPT,则表示中断处理程序是快速处理程序,快速处理程序被调用时屏蔽所有中断,而慢速处理程序不屏蔽。dev_id在中断共享时会用到,一般设置为这个设备的结构体或NULL.request_irq()返回0表示成功,返回-INVAL表示中断号无效或处理函数指针为NULL,返回-EBUSY表示中断已经被占用且不能共享。这两个函数分别要在初始化和释放模块中加载。

要在Linux申请了中断通道后,系统会响应外部中断IRQ_EINT0,从而进入中断处理序。中断处理程序功能就是将有关中断接收的信息反馈给设备,并根据要服务的中断的不同含义相应地对数据进行读写[7-8].所以FPGA中断处理的主要任务是:FIFO在接收到AD转换来的数据后,向ARM发出中断请求信号,让ARM来读取FPGA中FIFO状态寄存器的值,获取需要信息并安排接受数据,然后写状态寄存器清除相关中断位以继续响应中断,保证数据的有效传输。

中断处理程序的第一步是要先清除S3C2440A的中断悬挂寄存器和中断源寄存器相应的位。这是为了能够继续响应FPGA产生的中断。为了能够让FIFO能及时的接收到新数据,把写状态寄存器放到中断的一开始,即第二步就是写状态寄存器相应位,通过置1清除状态使AD中断能够继续产生。最后读取FIFO的数据。使用中断后数据的传输效率大大得到提高,能够满足实际的采集需要。

4.结束语

本方案中的采集板充分利用了ARM的灵活性和FPGA的并行性的特点,实现了适用于高速数据采集板的设计。方案采用S3C2440A作为主控芯片,通过千兆以太网接口实时地将采集的数据传输到上位机PC机,上位机可实时控制目标数据采集。FPGA芯片在控制A/D转换芯片的同时,将数据存储在SRAM中,并通过DMA接口与S3C2440A进行数据传输。实验表明,本采集板的实时性和高速性能够满足系统的设计要求,可广泛应用于各种数据采

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)