基于MicroBlaze软核的SOPC系统设计

,在本文设计的处理器系统中,每一个处理器都有自己独立的系统总线,因此,所有的存储器和外围设备与共享元素都是分开的。也就是说,不同总线上的相同外围设备可以有相同的地址范围。在每一个处理器子系统中,为了能够运行可执行文件,对存储器映像有一些要求。每个处理器都必须将自己的可执行文件加载到各自私有的MPMC地址空间中,可执行文件加载地址不能重叠。在私有存储器里必须有各自的复位和中断存储器映像,这种私有存储器可以通过本地存储器接口(XCL)或者PLBv46总线接口连接起来。一旦私有存储器与其他总线连接完毕,XPS的地址发生器会为每一个MieroBlaze处理器子系统(包括外围设备和存储器)生成适当地址范围的存储器映像。

1.2.3 处理器之间的通信与同步

在Xilinx SOPC系统设计中,常用的处理器之间的通信模块是Shared Memory和Mailbox,同步控制模块是Mutex,调试模块是MDM。

Shared Memory共有两个通信端口,它通过存储器控制端口分别连接到系统的两条PLBy46总线上。系统通过处理器对Slhared Memory模块进行读写操作完成通信。Shared Memory可以由片上本地存储器或者外部存储器构成。当信息传输量比较大时,Shared Memory的异步传输效率比较高,它支持零拷贝或者原状信息队列拷贝。

利用Mailbox也可以进行处理器之间的通信。关于Mailbox,有如下一些特征描述:

①Mailbox可以认为是处理器之间的类似于TCP/IP的一个简单的通信协议。

②处理器之间通过Mailbox通信有同步和异步之分:同步主要体现在处理器之间的通信上,接收者实时地读取Mailbox中的数据;异步主要体现在处理器之间的中断上,发送者通过Mailbox发送中断信息给接收者,接收者收到中断后反馈给发送者。

③每一个Mailbox核都有一个FIFO和一个双端队列,分别用来发送和接收信息,用户可以根据自己的需要对它们的深度进行配置,主要通过分布式的RlAM或者BRAM来实现。

④Mailbox共有两个端口分别连接到系统的两个总线上来实现处理器之间的通信。

⑤Mailbox软核比较适合传输信息量小于100字节的信息,发送者需要从本地或者外部存储器拷贝整个信息到FIFO,然后,接收者同步地拷贝整个信息到自己的存储器中,因此,Mailbox不适合传输信息量较大的信息,这些将会耗费掉处理器的一些时钟周期。

⑥处理器间的中断是指一个处理器去中断另一个处理器的行为,通过Mailbox的异步通信来实现,处理器发送中断就是往Mailbox里写入一个信息,然后Mailbox通过中断控制器对接收者产生一个中断,接收者收到中断以后会反馈给发送者,当Mailbox中没有新的信息时,中断为无效状态。

本文在SOPC系统设计中,用到的同步控制模块是Mutex。此模块主要有以下特点:

①存储器映像以后,Mutex寄存器的数量可配置这些寄存器中有分别存储数据和处理器ID的区域,Mutex寄存器中的数据和ID分别通过Mutex进行测试和设置。

②复位时,Mutex的值变为0,它表示Mutex处于开锁状态(UNLOCK),并且其中的处理器ID号没有赋值,当Mutex处于锁定状态(LOCK)时,其中的值保持不变。

③处理器通过软件赋值的方式将各自的处理器ID号写入到相应的Mutex寄存器中,从而获得Mutex的使用权,当两个处理器同步访问Mutex寄存器时,每个处理器都会读取Mutex寄存器中的值,然后和自己的ID号进行比较,比较匹配的处理器才可访问Mutex寄存器,修改其中的数据。

MicroBlaze核通过处理器调试口与MDM(Microprocessor Debug Module)调试模块相连。调试模块MDM可以调试系统中的每一个处理器。 MDM的特点如下:

①MDM的调试端口数目是可配置的,最多可以达到8个。

②MDM提供一个JTAG UART接口通向系统中的某个处理器,这个UART接口是通过PLBv46总线接口连接到处理器上的。

③MDM不会自动地调试每个处理器,用户必须通过输入调试命令来进行选择性的调试。

1.3 软件设计

1.3.1 存储器映像

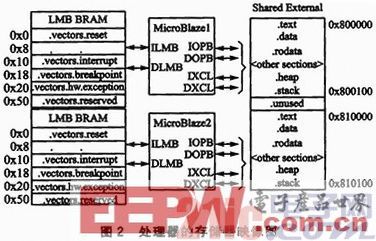

为了保证每个处理器在执行软件部分时不发生冲突,必须对其存储器进行存储器映像。图2是存储器映像图。

从图2中可以看出,用户可以灵活地为两个ELF文件分配适当大小的存储器空间作为ELF文件的映射地址范围。由于boot(引导)存储器不可以共享,所以ELF文件的boot部分(.vectors*)被映射到私有存储器中,它可以实现MicroBlaze处理器随时调用,也可以引导ELF文件加载到DDR中。Heap和stack的范围表示ELF文件在DDR中映像的存储器大校boot存储器的大小表示boot部分所能引导的DDR的范围。ELF文件的位置和输出链接脚本的位置可以根据用户的需求选择。每个可执行文件的存储器映像地址都是通过编译

MicroBlaze SOPC 相关文章:

- 双MicroBlaze软核处理器的SOPC系统设计(01-27)

- MicroBlaze在硬件加速中的应用技术(06-05)

- 基于Microblaze软核FSL总线的门光子计数器设计与实现(06-05)

- 全新EDK8.1简化嵌入式设计(06-04)

- 符合ISO/IEC18000-6C标准的RFID读写器数字基带系统设计(06-04)

- 基于MicroBlaze的AXI总线实时时钟IP核设计(12-13)