基于MicroBlaze的AXI总线实时时钟IP核设计

MicroBlaze是可以嵌入到FPGA中的RISC处理器软核,具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、军事、高端消费市场等领域。Xilinx公司的MicroBlaze 32位软处理器核是支持CoreConnect总线的标准外设集合。MicroBlaze处理器运行在150 MHz时钟下,适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

AXI是ARM公司提出的AMBA3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。AXI 总线技术不但使片上系统面积更小功耗更低,同时还获得了更加优异的性能。AXI 能达到这样的技术指标的一个主要原因,就是它的单向通道体系结构。单向通道体系结构使得片上的信息流只以单方向传输,减少了延时。AXI 技术满足超高性能和复杂的片上系统设计的需求,因此AXI的与应用也越来越广泛[1]。随着ARM公司与Xilinx公司的合作逐步加强,Xilinx开始逐步在FPGA产品中大力推广AXI总线技术。AXI在Xilinx公司的MicroBalze等CPU上面得到越来越重要的支持,必将成为未来的主流技术。

1 IP核的创建与导入

Xilinx的MicroBlaze软核为用户提供了大量的可用IP核,方便用户开发缩短开发周期,降低成本。但是用户的需求千差万别,官网提供的IP核不可能满足所有人的需求。因此开发环境支持用户自定义IP核,根据用户的不同需求,用户可以通过定制的方式开发自己需要的IP核。在测控装置的研发过程中,笔者发现插件上设计的RTC时钟芯片,虽然具有掉电保持时间的功能。但是在完成装置界面对时等功能时,对RTC芯片的读写操作显示到界面上后,会有一定的延时,界面无法精确的显示当前的时间。因此设计一个通过自定制IP核的形式,实现实时时钟时钟的功能解决上述问题。开发环境中的Xilinx Platform Studio为IP核的定值与导入提供了向导。

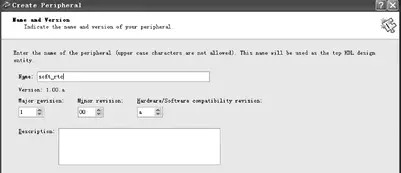

创建IP核的步骤如下:选择Hardware→Create or Import Peripheral Wizward来打开创建和引入外设向导。单击Next按钮。选择Create templates for a new peripheral。默认情况下新的外设将被存在pcores文件夹中方便查找。然后再次单击Next按钮。在Create PeripheralName and Version对话框中,输入定制的IP核的名字,这里输入本次定制IP核名称为soft_rtc。下面是版本控制,可以根据需要修改。界面如图1所示。

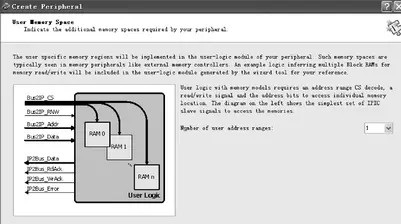

单击Next按钮,在Create PeripheralBus Interface 对话框中,选择AXI4,这是新的外设将要连接的总线。对于简单设计可以选择AXI4_Lite;下一步在IPIF (IP 接口) 配置,这里配置接口的一些属性,如是否是AXI 主/从设备等。所定制的IP是一个从设备,因而不需要使用主设备接口。数据宽度选择默认的32位,下一步选择需number of use memory ranges数量,这里选1。界面如图2所示。

接下来就是IPIC(IP 互联),也就是IP的接口信号。接下来需要使用需要使用BFM总线功能模型对外设进行仿真,本例不要使用。最后,需要选择HDL类型、ISE工程支持和软件驱动模板。此处使用Verilog模板,选择后需IP接口仍然是VHDL编写,只是用户逻辑改用Verilog。如果不需要使用软件驱动模板,可以不选。最后给出了外设的信息summary。完成上述步骤后,自定制的soft_rtc IP核的模版创建完成,只需根据需求对user_logic文件索要实现的功能编写应用代码,并配置相应的引脚。

完成user_logic的代码编写后,需要将完成的IP核导入工程。大致步骤如下:再次使用Hardware Create or Import Peripheral, 并单击Next按钮。选择Import existing peripheral项,单击Next按钮再次输入名称soft_rtc,单击Next按钮,选择Yes按钮。下一步选中第一项HDL source files单击Next按钮,然后下一步骤选中第二项Use existing Peripheral Analysis Order files(*pao), Browse到相应的目录下,选中.pao文件,单击打开,然后单击Next按钮;出现图3所示的窗口时,选中左侧AXI4Lite选项,然后单击Next按钮后面都选择默认选项直到出现结束窗口时选择结束按钮Finish按钮。 这样通过上述步骤完成了IP核的创建与导入。最后将IP核加入到工程中与AXI4Lite总线连接。完成IP核模版的创建与导入后,下一步就要进行完成IP核user_logic文件的代码设计。

2 soft_rtc IP核的设计

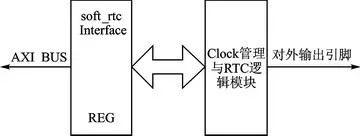

soft_rtc IP核中主要分为与上层接口的寄存器管理模块、为IP核提供精确时钟的 Clock分频模块和RTC的核心逻辑模块[2]。IP核接口如图4所示。

开发板上提供有25 MHz的晶振和16.384 MHz的晶振。为了计时的精度,将16.384 MHz的输入信号引入soft_rtc模块。Clock 分频模块将输入的16.384 MHz准晶振时钟4分频

MicroBlazeAXI总线实时时钟IP 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)