浅谈CPLD在IGBT驱动设计中的应用

障信号,以确保系统工作的稳定性。

3 CPLD的实现

20世纪90年代,引起数字系统设计方式发生突破性变革的技术是VHDL设计技术。VHDL Very High Speed Integrated Circuit VHSIC Hardware Description Language作为IEEE-1076标准所规范的硬件描述语言,非常适用于可编程逻辑器件的应用设计,并正在得以普及。采用自顶向下的设计方法,是用VHDL设计系统硬件最突出优点之一。

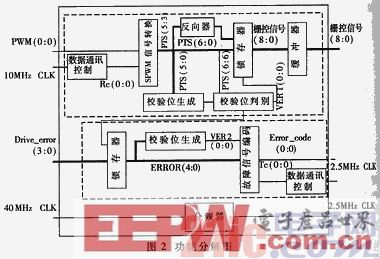

通过前面对数据流和通讯方案的分析,按照自顶向下的原则,我们对信号处理单元进行功能分解,将其分解到下面的各个单元中,见图2。通过功能分解,我们可以看到,单元内部构造可以分为三个部分:一部分对栅控信号进行处理;另一部分对故障信号进行处理;最后一部分用于产生控制故障信号发送的时钟。

从图2我们可以发现栅控信号处理部分与故障信号处理部分都含有功能相同单元:校验位生成单元、数据通信控制单元及锁存单元,因此可以对以上这些单元进行参数化设计。在参数化设计以前,我们还需要构造一些公共的基本元件,如触发器、寄存器、计数器和同步器等。这以后,我们就可以对前面提到的功能相同的单元进行参数化设计。

在进行参数化设计以前,我们需要对各功能单元的输入输出信号进行分析以确定信号使用的数据类型。由于IGBT控制问题的特殊性,在这里我们统一使用Bit和Bit-vector型数据。Bit型数据只有两种状态:“0”和“1”,可以有效地防止多态数值系统给控制和编程带来的麻烦。

在进行传统的电子线路设计时,设计师的工作是按电路原理图将各个单元电路和器件连接起来,形成一个完整的系统。而在利用VHDL设计电路时,设计师所要完成的不过就是将那些用VHDL语言描述的单元电路和器件连接起来。在这个意义上,利用VHDL语言进行设计与利用传统方法设计没有太大的区别,但采用自顶向下的设计方法时,VHDL具有无可比拟的优越性。作为一种硬件描述语言 VHDL语言有别于一般的计算机语言。它既有并行执行的语句,又有只能顺序执行的语句。利用VHDL这种特性,我们可以将整个系统分成若干个相对比较独立的模块来进行电路设计。在下面的程序中,进程COUNTER描述了一个16位计数器,它通过对40MHz时钟进行分频,产生进程CONTROLLER所需的2.5MHz时钟。进程CONTROLLER构造了一个发送控制计数器,它通过对进程COUNTER所产生的时钟信号进行计数,产生故障信号的发送控制信号。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)