基于ARM+FPGA的视频采集处理系统设计

有6个控制信号。其中MCLK由FPGA产生,是传感器工作时钟输入;FVAL是帧有效信号,它的上升沿表示一帧数据的开始。在FVAL信号的有效期间内包含了480个行有效信号LVAL,而每个LVAL信号的高电平期间包含了数据总线上640个像素数据的输出。所以,在FVAL一个周期内,图像传感器正好输出了完整的一帧图像。分辨率为640×480。仅当FVAL和LVAL信号同时为高电平时,传感器输出数据 D[9:0]有效,FPGA在每个像素时钟PIXCLK上升沿时将有效数据读入。经实测,传感器正常工作时,SCLK,LVAL频率约为7.56kHz和 14.2kHz。

本系统采用Verilog HDL语言来编写CMOS图像传感器的时序驱动。在实际设计中,把控制模块分成两部分:I2C_Config模块根据设定的曝光时间来发生I2 C总线SCLK和SDAT时序,而Capture模块则负责与传感器的数据接口,读入10位的图像数据,并送到下一级模块进行相应处理。以下是 Capture模块部分代码:

always@(posedge iCLK or negedge iRST)

begin

if(!iRST)

……… //各信号清零复位

else

begin

Pre_FVAL <= iFVAL;

if( ({Pre_FVAL,iFVAL}==2'b01) && mSTART )

//当前帧有效且前一帧处理完

mCMOS_FVAL <= 1;

else if({Pre_FVAL,iFVAL}==2'b10) //正

在处理前一帧

mCMOS_FVAL <= 0;

mCMOS_LVAL <= iLVAL;

mCMOS_DATA <= iDATA;

//读取数据送入FPGA

if(mCMOS_FVAL)

//帧有效

begin

if(mCMOS_LVAL)

//行有效

begin

if(X_Cont<639)

X_Cont <=X_Cont+1;

else

begin

X_Cont <=0;

Y_Cont < = Y _

Cont+1; //计算像素坐标,方便后续模块显示

图 3

3.2 格式转换模块

从数字图像传感器传来的原始图像质量,在整个系统的性能影响中占主要地位,对后续的视频压缩和传输速度有着非常重要的影响。后期将会在采集前端加入相应的图像处理算法。而大多数处理算法都是基于RGB颜色空间的,为了进行视频压缩以减小数据量,就需要进行RGB到YUV的颜色转换。

YCbCr是YUV属于颜色空间的一种储存格式,适用于MPEG、JPEG等格式的编码。相比RGB色彩空间,YCbCr色彩空间有一个显著的优点。Y的存储可以采用和原来画面一样的分辨率,但是Cb,Cr的存储可以使用更低的分辨率。这样可以占用更少的数据量,并且在图像质量上没有明显的下降。所以,将色彩信息以低于量度信息的分辨率来保存是一个简单有效的图像压缩方法。

在ITU-R BT.601标准中,建议在计算Y时,权重选择为kr=0.299,kg=0.587,kb=0.114。于是常用的转换公式如下:

Y=0.299R+0.587G+0.114B

Cb=0.564(B-Y)

Cr=0.713(R-Y)

采用硬件描述语言进行编程之前,需要消除浮点数运算。合理利用硬件资源是编写代码时要充分考虑的。对于常系数乘法单元,其占用的LEs(Logic Elements)与系数大小有关。为了避免出现负数和溢出问题,最终采用的转换公式如下:

Y = [CA*27] *(R - G)+ G + [CB*27] *(B - G)+ YOFFSET

Cb = [CC*27] *(B – Y)+ COFFSET

Cr = [CD*27] *(R – Y)+ COFFSET ([ ]符号表示取整运算)

各参数的取值见表1[2]。

表1 各参数值

CA0.299 CC0.492

CB 0.114CD0.877

YOFFSET 16 COFFSET 128

3.3 图像压缩控制

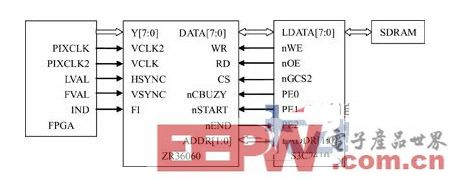

ZR36060的控制接口示意图如图3所示,VCLK和VCLK2是需要外部提供的时钟信号,由FPGA产生的PIXCLK为25MHZ,满足系统要求。 VCLK是VCLK2的分频,并要求与VCLK2同步。

本系统选择ZR36060工作状态为:8位代码从模式,视频同步从模式,8位视频总线宽度。ZR36060的接口可分为视频接口、主机接口和代码接口三部分。视频信号由视频接口Y[7:0]输入,主机接口通过DATA[7:0]对芯片内部寄存器设置,控制工作状态,压缩后的码流通过代码接口 CODE[7:0]输出到存储器中缓存。8位代码从模式下,主控制器的数据总线DATA[7:0]通过读写HostData对ZR36060的内部寄存器进行设置和读取,代码总线CODE[7:0]从CODEFIFO读写JPEG数据。行同步信号HSYNC接到图像传感器的LVAL引脚,场同步信号 VSYN接到传感器的FVAL引脚。奇偶场指示信号由FPGA给出,每采集到FVAL的上升沿,IND信号翻转一次,以指示奇偶场。

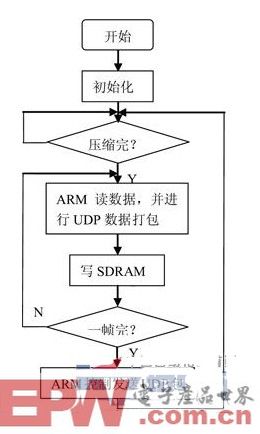

3.4 以太网数据传输

本系统采用UDP/IP协议来实现图像数据的网络传输。压缩后的图像数据经ARM进行UDP数据打包后,存储在SDRAM中。一个完整的数据帧格式包括以太网头、IP头、UDP头和一行图像数据,其系统工作流程图见图4所示。ZR36060 每压缩完成一帧,就由S3C2410读取并写到SDRAM中,然后判断是否读完一帧图像数据,读完后则发送UDP包,将图像数据通过以太网发送到网络。

图 4

4 小结

本文

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)