基于LEON3处理器动态图像边缘检测的SoC设计

熵值小于阈值时,输出1。这样就得到一幅二值化后的边缘图像。至此,完成了整个局部熵边缘检测算法的硬件实现。

3.2 自定义IP接口设计

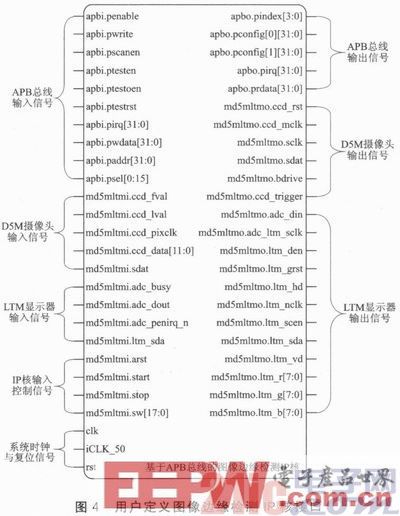

自定义IP核包含以下几个主要部分:图像采集(D5M摄像头接口);图像制式转换;图像存储;图像显示(LTM显示接口);图像边缘检测模块;自定义寄存器。

图4给出了基于APB外围低速总线所设计的图像边缘检测IP核的外部接口信号图。由图中可知,此IP核的接口信号可分为:

①系统时钟与复位信号:是整个LEON3架构所共用的时钟信号和复位信号,而iCLK_50是由外部直接引入的频率为50MHz的时钟,未经过PLL处理。

②IP核控制信号:主要实现IP核的触发功能和结束功能。

③APB总线的输入信号和输出信号:此信号主要用于APB总线控制、IP核选择、IP核使能等,其中包括对IP核内部寄存器的设置都是通过APB总线信号来完成的。

④D5M摄像头输入信号和输出信号:此信号主要完成对D5M摄像头的配置以及数据采集。

⑤LTM显示器输入信号和输出信号:此信号用于对LTM显示器的配置。由于基于APB总线的IP核集成D5M摄像头、LTM显示器和边缘检测算法于一体,所以外部接口信号相对较多。但就APB总线本身而言,其信号并不多,这也是基于APB总线的设计方法相对简单的原因。

3.3 自定义IP核的结构设计

有关“基于APB外围低速总线图像检测IP核的实现基本思想部分”略——编者注。

基于APB总线的IP核框架结构如图5所示。

4 实验结果

4.1 动态图像边缘检测算法硬件实现仿真与分析

文中首先利用Matlab验证局域熵边缘检测算法设计的正确性,然后采用Verilog HDL硬件描述语言编写图像边缘检测算法,在算法实现过程中,为提高算法的性能,采用了Quartus II中自带的DSP加速宏模块。同时,为验证仿真算法的正确性,编写Testbench系统测试文件,对其进行仿真验证,图6为局域熵边缘检测算法的硬件仿真时序图。

从图6中,可以看到3×3窗口产生的过程,L1~L3为采用片上缓存的方法实现的三行数据的同步。X1~X9对应3×3窗口中的9个像素点。图中最终的数据输出是有一定时延的,这是由于算法中存在大量的乘加运算和浮点数运算造成的。

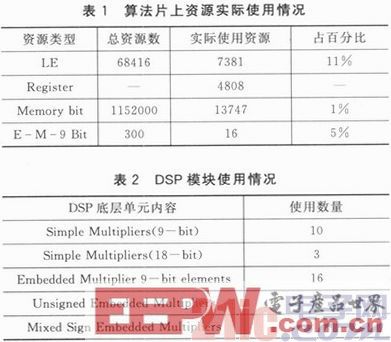

在实现算法的同时,考虑到所选芯片提供了可用于加速算术运算的DSP模块,于是为了加速算法的处理速度,在算法实现过程中,加入了大量的DSP加速处理模块,如乘加器,浮点除法器等。表1给出了用硬件语言实现上述算法所使用的芯片资源情况。表2给出了该算法对DSP加速模块的使用情况。

4.2 动态图像边缘检测SoC系统性能测试

测试采用的硬件开发平台为FPGA CycloneIIEP2C70F896C6N,Quartus II版本为10.0(32位),LEON3开发包版本为grlib-gp1-1.0.22-b4095.zip。D5M摄像头工作在25MHz频率,所采集的图像分辨率为400×240,R、G、B每种色彩以10-bit二进制数据表示,D5M摄像头每秒采集22~25帧图像。LTM显示屏的显示分辨率为400×240,工作在33MHz频率。

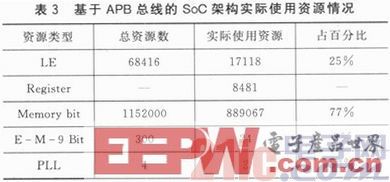

表3为测试得到的片上资源使用情况。图7为文中设计的动态图像边缘检测SoC系统工作实物图。从其结果可以分析得到,文中设计的动态图像边缘检测SoC占据的片上资源在可以接受的范围内。

且由实际测试可知,在外界环境适中的条件下,系统可以得到很好的图像边缘检测效果。但由于图像的分辨率较大,而边缘检测算法中所采用的窗口为3×3,相对于图像来说较小,所以图像上的一些小的阴影区域也会被检测出来,形成阴影区域干扰,影响图像的边缘检测效果。但总体来说,实现了动态图像边缘提取的最终目的。

结语

本文介绍了基于LEON3开源软核处理器的动态图像边缘检测SoC设计。

实验结果表明该SoC系统工作正常,可以实现每秒22~25帧,最佳分辨率为400×240和640×480的动态图像边缘检测功能,平均数据延时在70~80个系统时钟。系统具有很好的可移植性与可配置性,占用资源少,速度快,具有广泛的应用前景。

- SPARC微处理器综述(05-29)

- SPARC V8结构嵌入式微处理器开发环境的设计实现(09-18)

- SPARC高性能处理器集成开发环境及其编译器设计与实现(02-14)

- 基于BM3803MG与VxWorks的BSP的设计实现(08-12)

- 欧比特:首家登陆创业板的IC设计公司(09-12)

- SPARC结构与实时内核的移植(05-17)