一种使用Cadence PI对PCB电源完整性的分析方法

放位置,使电源分配系统阻抗在PCB系统的整个工作频率范围内都小于目标阻抗成为解决电源完整性问题的关键。借助Cadence PI可以快速地确定去耦电容的容值、数量和摆放位置,提高开发效率。

2 电源完整性仿真

2.1 ARM11核心系统

文中以Cadence PI为仿真工具,对ARM11核心系统进行电源完整性分析,本文中的ARM11核心系统采用S3C6410芯片。S3C6410是一款ARM11体系架构,FBGA封装,需要多电源工作的芯片。本文中该芯片有2个工作电压:核心供电电源1.2 V,有26个电源引脚(10个核心电源引脚,16个逻辑电源引脚);输入/输出接口供电电源3.3 V,有30个I/O电源引脚。芯片内部的工作频率是667 MHz,外部存储器输入/输出接口工作频率是266 MHz。ARM11核心系统采用8层层叠结构,在信号仿真阻抗匹配和生产标准的前提下,设定层间间距。本文利用Cadence PI对ARM11核心电压电源网络VDD_ARM进行电源完整性仿真。

由S3C6410芯片数据手册可知,核心电流消耗是200 mA,加上100%的容限,系统允许的电压波动值取4%,核心电压1.2V,根据式(1),在仿真中设定目标阻抗为0.12 Ω。

2.2 电源完整性仿真

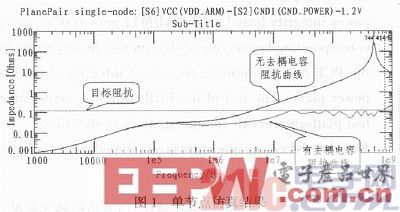

2.2.1 单节点仿真,分析验证并优化电容选择

在单节点仿真中,忽略电源系统中各元件实际的物理连接,假设电源调压模块VRM、仿真激励源、电流源和所有电容都并联在一起,单结点仿真可以得到维持目标阻抗所需要的电容。VDD_ARM电源网络单节点仿真结果如图1所示,所有电容有效时(下面曲线)和所有电容无效(上面曲线)电源分配系统的阻抗,目标阻抗(中间直线)。最后选择0603贴片封装,150 pF电容4个,390 pF电容3个,0.1μF电容3个,4.7μF电容2个。

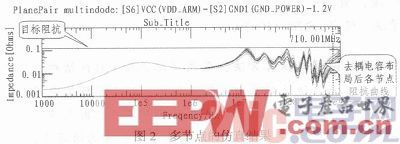

2.2.2 多节点仿真,放置去耦电容优化布局

由于单节点仿真没有考虑去耦电容的布局,为了获得更精确的结果,考虑噪声源和去耦电容的放置位置,在全频率范围内进行多节点仿真。在多节点仿真时,Cadence PI根据用户定义将电源平面分隔成多个网格,并对每一个网格进行建模,然后将放置的去耦电容、电压调节模块VRM和噪声源与具体的网格点连接起来,产生每一个节点的频率-阻抗仿真波形。

为获得较高的精确度,网格尺寸大小必须大于系统最高频率对应波长的1/10。波长计算如式(3):

本系统最高频率为667 MHz,电路板材料是FR-4,介电常数为εr=4.5。由式(3)计算得到λ为212.033 mm。VDD_ARM电源平面为80 mm×70 mm,选择44可精确分析,为了便于分析,本文选择88的网格。放置电容时,电容的有效去耦半径是一个比较重要的参数,根据经验数据,这一半径在实际应用中的取值最好小于λ/50。不断进行多节点仿真,使得所摆放的电容数目最小化。图2为VDD_ARM/地平面对多节点的仿真结果。从结果可知,在放置相应的去耦电容之后,除极个别点外,平面阻抗在小于710 MHz的范围内都是小于目标阻抗的,而ARM11核心系统的最高时钟频率为667MHz,因此此次去耦电容的布局完全满足要求。

2.2.3 电源平面静态IR-Drop直流压降分析

芯片要正常工作需将供电电压限定在允许的波动范围之内。电源波动是由DC损耗和AC噪声两部分造成的,直流压降DC IR-Drop是产生DC损耗的主要原因。静态IR-Drop直流压降主要与金属连线的宽度及所用层、该路径所流过的电流大小、过孔的个数和位置有关。在Cadence PI中设置电源供给管脚和灌电流后,对布局布线完成后的ARM11核心供电电压网络VDD_ARM进行直流压降分析,当ARM11核心系统工作频率为667 MHz时,其1.2 V的直流电压的允许波动幅度为+/-0.05 V。Cadence PI仿真软件计算出VDD_ARM网络电压梯度,其中Drop的最大值为0.013 V,小于允许波动的幅度为+/-0.05 V,完全满足S3C6410工作电压要求,可以保证系统工作的稳定性。

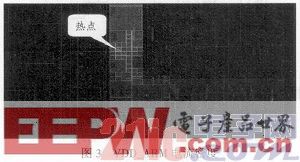

2.2.4 电源平面电流密度分析

当电源平面上过孔过多或者分布不合理时,会出现电流流过狭窄区域,从而造成该区域电流密度过大。电源平面上最大的电流密度区域称之为热点,热点有可能会导致严重的热稳定性问题,因此要合理地设计过孔,使板的电流密度分布均匀,避免在关键芯片和高速走线附近出现热点。图3为VDD_ARM网络电流密度分布,图中标注点为该平面热点,其位置周围为一块空白区域,平面其他部分电流密度较均匀。

3 PCB电源完整性测试

在第1版PCB中,没有利用Cadence PI分析,只是根据经验放置了一些去耦电容。在调试时,发现高速数字信号的波形不好,有时会有误码。在第2版中,通过Cadence PI进行分析,对去耦电容的数值数量和位置,部分原件的布局布线进行了调整。

利用动态电子负载模拟高速

- 基于FinFET的SoC系统设计(02-11)

- 真实环境中的系统设计(09-09)

- 闪存革命无处不在(12-25)

- 设计自己专用处理器该怎么完成?(07-11)

- Cadence发布完整数字与签核参考流程(12-05)

- 展讯使用Cadence Innovus设计实现系统加速设计效率(09-12)