一种基于FPGA+DSP的通用飞控计算机平台设计

时,根据串口通信的特点,首先判断低电平起始位。检测到起始位之后,按照严格地每八个时钟一位的关系采集一个字节8位的电平。由于噪声的存在可能会导致采集到的瞬时电平有误,此时采用表决机制,即在8个时钟期间采样3次,以其中2次相同的电平为准。实验证明,表决机制能极大排除随即噪声干扰,降低串行通信的误码率。接收到数据之后存储在对应的双端口RAM中,等待DSP读龋串口数据接受流程如图2所示。

数据发送时先从双端口RAM中读出需要发送的数据,按照串口时钟,先发送起始位(低电平),再依次通过移位寄存器将8位的数据转换成串行的‘0’/‘1’发出。主要由下面语句实现:

txd<=txd_buf(0);

txd_buf(6 downto 0)<=txd_buf(7 downto 1);

其中txd是要发送的1位逻辑电平,txd_buf中存储着将要发送的数据。发送流程如图3所示。

将按照上述流程设计的程序在FPGA中进行测试。将FPGA串口和PC机连接,采用115 200波特率连续工作3分钟,收发均无错误字节。

3.1.2 双RAM缓冲机制

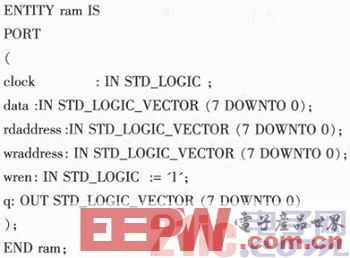

由于串口外设的波特率是115 200,属于低速外设,因此在串口数据和DSP之间采用双端口RAM作为缓冲区。由于此FPGA上自带片上RAM,因此可以利用开发环境自带的IP核生成片上双端口RAM,不用额外增加片外RAM器件(图1)。双端口RAM的实体定义和读写时序:

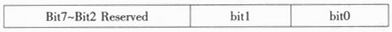

将每个RAM中的最后一个字节作为反映RAM存储状态的状态字。RAM的状态字代表的含义如下:

bit0:1-串口接收到新数据帧 0-无新数据帧;

bit1:1-数据已经被读取 0-数据未被读取;

惯导和导引头向弹载机每6 ms传输一帧数据,将数据存储到双端口RAM中,同时将bit0置‘1’,bit1清零,即RAM状态为“新数据帧未被读取”。由于惯导和导引头的数据不同步,因此DSP每1ms就查询一次RAM的状态字。若接收到新的数据帧(bit0=1),则读取RAM数据,并将“数据被读取”位置1(bit1=1)。这样,惯导和导引头给DSP发送的数据延迟不超过1 ms,可以认为惯导和导引头的数据是实时同步的。

在串口接收数据期间,如果串口和DSP在同一时间操作RAM,可能导致DSP读取到帧错乱的数据。为了保证数据帧的完整,不使两者同时读取RAM,采用双RAM缓冲机制,即为每个串口配置2个双端口RAM的作为缓冲,如图5所示。串口数据接收程序通过查询RAMa和RAMb的状态字,若bit1=1,则将接收到的数据帧存储到对应的RAM中,完成之后将bit0置1,bit1清0,这个周期为6 ms。与此同时,DSP每1 ms查询一次RAMa和RAMb,若bit0为1,则读取对应RAM中的数据帧,同时将bit0清0。bit1置1。串口数据发送过程与接收类似,数据传输方向相反。

采用双RAM缓冲机制,使得串口和DSP不在同一时间访问同一RAM区,避免了错帧和丢帧,同时保证了数据传输的实时性。

3.2 DSP软件设计

DSP软件设计采用模块化设计方式,分为应用层和底层软件两部分。应用层软件主要实现飞控流程和飞控算法;底层软件主要实现数据格式的转换,以便通过DSP总线和FPGA进行数据交换。

3.2.1 应用层软件设计

外部的惯导和导引头6 ms产生一次数据,DSP开启1ms的定时器中断,在中断中每1 ms查询一次双端口RAM的状态字,判断是否有新数据产生,这样采集的数据延迟不会超过1 ms。飞控解算的周期为6 ms,遥测数据发送的周期为12 ms,在定时器中断程序中完成飞控解算和遥测数据发送。

中断服务程序每1 ms运行一次,每次首先查询导引头和惯导有没有更新数据,再读取新数据存储在全局结构体里。每6ms用全局结构体里得到的新数据解算一次飞控指令,得到舵机的输出角度,输出舵控指令,控制舵机。流程如图6所示。

3.2.2 底层软件设计

DSP底层软件主要完成外部数据交换和数据格式的转换。DSP通过XINTF产生读写时序(图2图3所示时序),FPGA也设计与之相匹配的时序完成两者之间的数据交换。

DSP应用层软件使用的是浮点数,而DSP和FPGA之间只能传递二进制数,因此需要按照IEEE标准进行浮点数和二进制数之间的转换。根据IEEE标准,可以用32位,即8个字节表示一个浮点数。如果将代表浮点数的4个字节组合成32位的整型数inte32,进行强制类型转换皆可以得到浮点数,转换函数如下:

将浮点数转换成整型数的方法与此类似。底层软件按照上述方法实现数据转换,供应用层调用。

4 系统验证

弹载机实物设汁制作完成之后可以利用半实物仿真平台进行测试,该半实物仿真平台由上位机、惯导、舵机和三轴转台组成。如图上位机的作用是模拟导弹动力学模型和导引头信息,并控制三轴转台运动模拟导弹姿态。导弹的

- 基于DSP+FPGA的数字导弹飞控计算机设计(10-22)

- 基于FPGA的Bayer彩色自动白平衡设计与实现(06-05)

- 数据采集装置在某型控制器中的应用(01-21)

- 双端口RAM在单片机系统中的应用(03-08)