嵌入式软件跟踪信息嵌套缓存机制和解析机制的设计

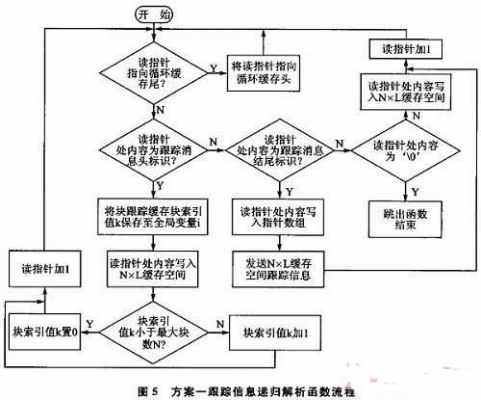

首先在PC端跟踪信息解析单元开辟一个环形队列(即循环缓存)用于存放串口输出的跟踪信息,通过一个读指针访问该循环缓存并进行递归调用解析。同时在PC端开辟一个大小为N×L的跟踪缓存空间(即N个长度为L的连续缓存空间)用于存放解析出的完整跟踪信息,每一块长度为L的缓存存放一条完整的跟踪信息。申请一个指针数组,用于保存每一个完整内存的起始地址,即记录N×L缓存中每次写指针的变化情况。跟踪信息递归解析函数流程如图5所示。

最后将解析完成的跟踪信息码流转换成为可见字符,在PC机上显示输出。

3 跟踪优化方案二

3.1 备份缓存管理机制

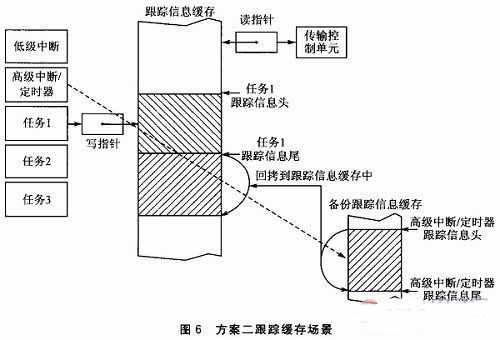

备份缓存管理机制采用含跟踪头和跟踪信息的跟踪信息帧格式,将跟踪信息写入一个大小为N的全局跟踪信息缓存中。为避免在任务切换频繁时当前任务被高优先级任务打断造成数据丢失,申请一个嵌套深度为M的备份缓存来存放高优先级任务跟踪信息。其中,备份缓存区域每块子缓存的长度均为m,设置跟踪忙碌标识位,初始值为0。跟踪源通过调用跟踪系统提供的跟踪接口函数,将跟踪忙碌标识置1,并将当前跟踪源跟踪信息填入全局跟踪信息缓存。完成当前跟踪信息写入操作后,将跟踪忙碌标识置0。若当前跟踪源在进行写入操作,即跟踪忙碌标识为1时,高优先级任务调用跟踪接口,则将高级任务的跟踪信息写入备份缓存中,当前跟踪源继续进行未完成的写操作。每次写完当前跟踪信息,检查备份缓存中是否有数——若有,则将备份缓存中的跟踪信息拷回至全局跟踪信息缓存中(跟踪缓存场景如图6所示),即在当前任务跟踪信息写入跟踪信息缓存时,若高级任务到来,则将高级任务跟踪信息进行封装并写入备份缓存。当前跟踪结束写入操作输出成功后,检查备份缓存中是否存在跟踪信息——若有,则将备份缓存中的跟踪信息回拷至全局跟踪信息缓存中,从而保证全局跟踪信息缓存中跟踪信息的连续性。

3.2 传输控制机制

同跟踪优化方案一中传输控制机制。

3.3 普通查询解析机制

根据跟踪缓存管理机制二,由于全局跟踪信息缓存中跟踪信息呈完整连续分布,解码方式采用遍历查询方式。

首先,在PC端跟踪信息接收单元开辟一个环形队列(即解析前循环缓存),用于存放从串口接收的跟踪信息。

然后在PC端解析显示单元开辟一个解析后循环缓存,用于存放解析后的完整跟踪信息。使用读指针遍历解析前循环缓存,查询到以跟踪头标识X开头的字符串,将其后的完整跟踪信息写入解析后循环缓存中,直至下一次遇到跟踪头标识X,记录解析前循环缓存读索引并保存当前解析后循环缓存写索引。循环以上操作,将解析前循环缓存中的跟踪信息依次解析,并放入解析后循环缓存中。

最后将解析后循环缓存中解析完成的完整跟踪信息码流转换成为可见字符,在PC机上显示输出。

4 性能分析比较

4.1 跟踪优化方案一

将跟踪信息按物理连续存储方式存储数据,即跟踪源在单条跟踪信息组装过程中,通过全局写指针控制跟踪信息写入。所有跟踪点均跟踪当前优先级秩序,对跟踪信息缓存区进行写操作,保证仅有一个跟踪信息缓存,且跟踪源相互抢占时根据优先级高低对跟踪缓存进行写操作。该机制跟踪缓存中的跟踪信息呈现嵌套、打断的不完整码流。

跟踪信息发送机制采取跟踪接口函数中触发传输装置搬移数据。在传输控制单元,通过配置DMA总线,将全局跟踪信息缓存中的跟踪信息搬移至串口寄存器中。PC端接收装置从串口寄存器中取出数据,放入PC端解析单元缓存空间,通过跟踪信息递归解析机制,将不完整的跟踪信息解析为完整连续的跟踪信息。其中每个跟踪信息缓存区尾部都设置一个保护数据区,保护区长度为单条信息最大长度L。

该方案解决了跟踪信息丢失问题,在PC端解析显示单元对不连续码流进行解码。由于该机制在嵌入式跟踪缓存单元中采取物理连续存储数据方式,降低了跟踪软件对ARM系统资源的消耗,保证了在高速运行情况下跟踪系统对ARM处理器CPU的消耗尽可能低。从而避免在高速运行的系统中,由于跟踪系统占用大量CPU导致系统运行速率低。该方案适用于对ARM子系统运行速率要求较高的终端系统。

4.2 跟踪优化方案二

在嵌入式跟踪信息缓存单元申请一个全局跟踪信息环缓存空间,同时申请一组备份缓存。写指针冲突时,高级任务的跟踪信息被写入备份缓存中,当前跟踪源继续将其跟踪信息写入全局跟踪信息缓存。每次写完当前条跟踪信息,检查备份缓存中是否有数——若有,则将其拷回至全局缓存中。该机制根据任务优先级高低来管理写指针,解决了写指针冲突导致跟踪信息不连续的问题。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)