MSP430:MCLK、SMCLK、ACLK默认时钟频率

一、MCLK、SMCLK、ACLK默认时钟频率

1.1 POR与PUC

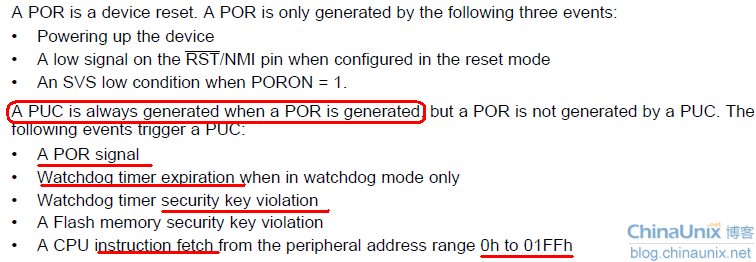

POR指Power-On Reset,即上电复位(硬件),PUC指Power-Up Clear,即上电清除(软件复位),这是MSP430两种分离的复位信号。POR总会引起PUC,关于POR与PUC的触发条件见用户指南,如下:

图1 POR与PUC触发条件

1.2 默认时钟频率

有两种方法(甚至更多)可以得知MCLK、SMCLK、ACLK默认的时钟频率。

(1)通过用户指南描述

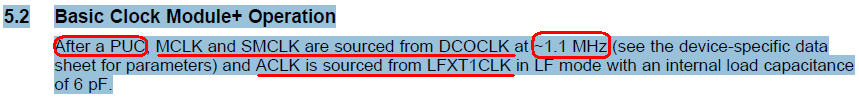

查阅用户指南可得到系统复位后,时钟信号MCLK、SMCLK、ACLK的时钟源分别是DCOCLK(数控震荡器)、DCOCLK、LFXT1CLK(低速晶体震荡器)。如下:

图2 复位后默认时钟频率

(2)通过寄存器初始值判定

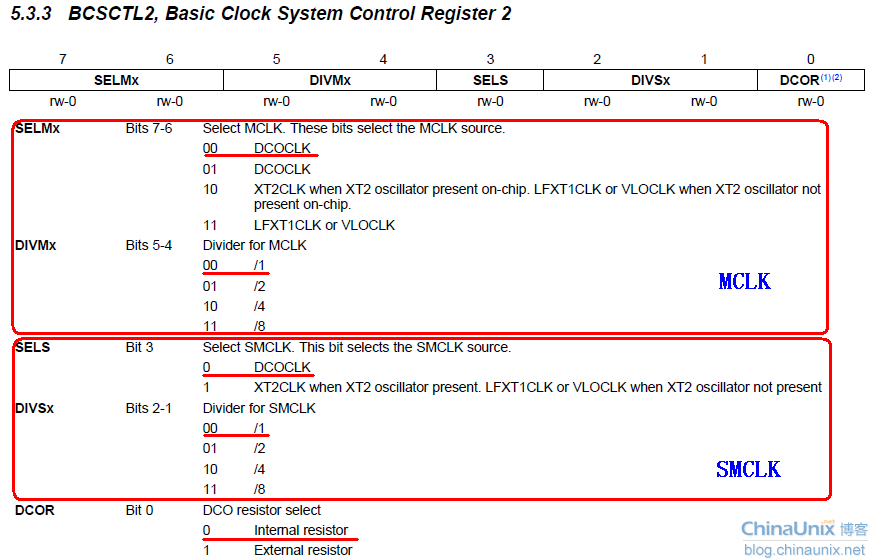

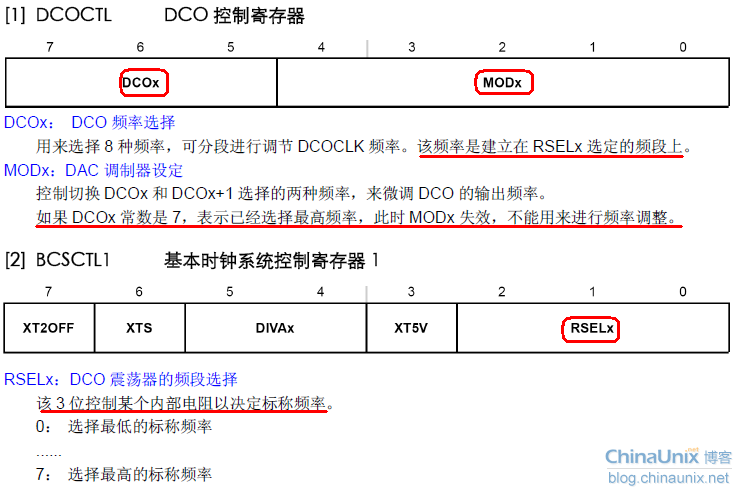

用户指南会给出每个寄存器的初始值,通过分析初始值各位的含义,并对照数据手机,也可得到其默认频率。定位到用户指南基本时钟模块(Basic Clock Model),其寄存器描述如下:

结合图5分析,可知RSELx为7(BCSCTL1低3位),DCOx为3,MODx为0,再对照图4可知系统复位后MCLK和SMCLK的频率在0.8MHz~1.5MHz,即819.2KHz~1536KHz。再结合图3基本时钟系统控制寄存器2(BCSCTL2),可知MCLK默认时钟源是DCOCLK,SMCLK默认时钟源也是DCOCLK。BCSCTL2示意图如下:

图3 BCSCTL2示意图

1.2.1 MCLK和SMCLK时钟频率

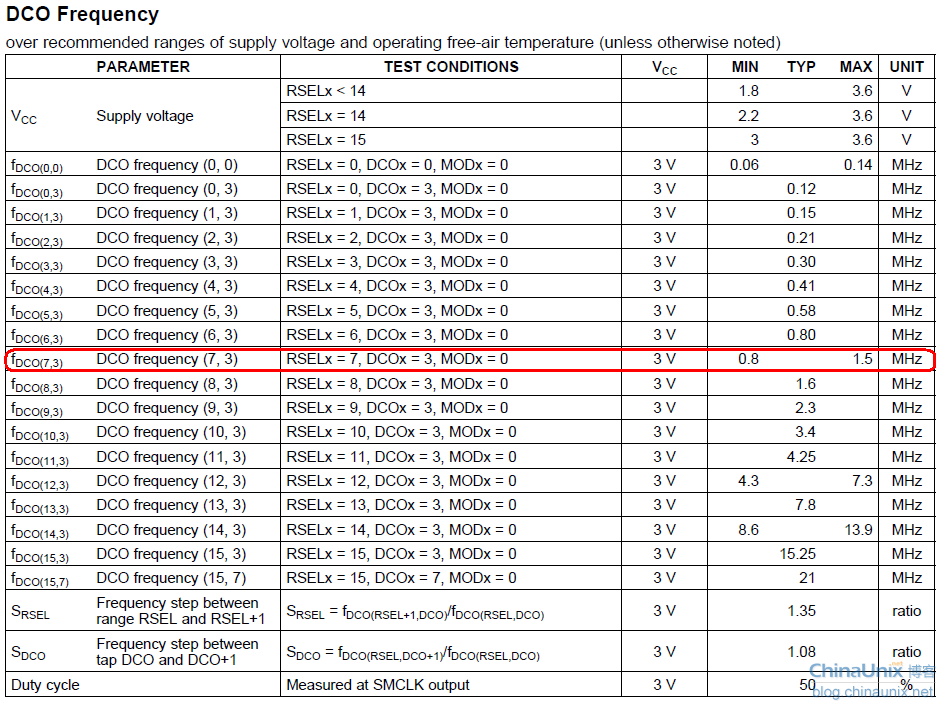

在数据手册可以找到DCO频率表(搜索关键词DCOCLK可快速找到),如下:

图4 DCO时钟频率

由上图可知,系统复位后MCLK和SMCLK的频率在0.8MHz~1.5MHz,即819.2KHz~1536KHz。系统启动后,可以调整RSELx(基本时钟系统控制寄存器1BCSCTL1前3位)、DCOx(DCO控制器DCOCTL前5位)、MODx(DCO控制器DCOCTL后3位)的值得到合适的频率,示意图如下[3]:

图5 DCOCTL和BCSCTL1示意图

注:图5跟用户指南有一定出入,MSP430G2231的BCSCTL1位0~4都是RSELx,但因是中文比较直观,就没换了。

1.2.2 ACLK时钟频率

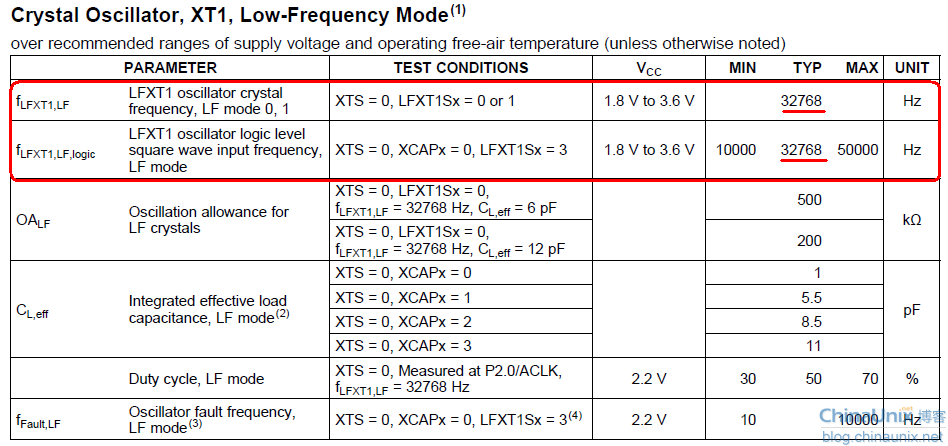

同理,可以从数据手册查得ACLK时钟源LFXT1CLK时钟频率如下:

图6 LFXT1时钟频率

由上图可知,系统复位后ACLK的频率典型值是32768Hz,即32KHz。

二、应用举例

2.1 FLASH时钟设置

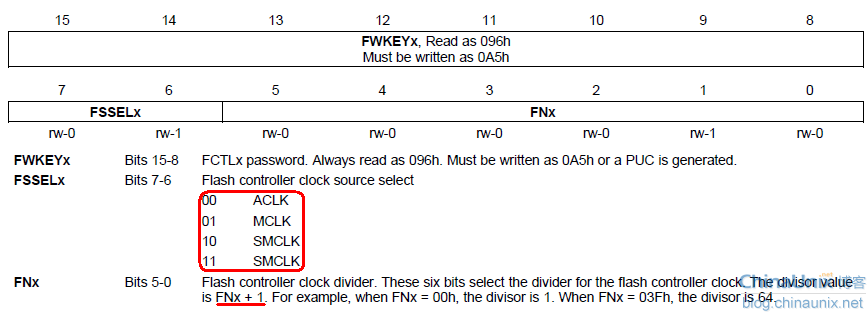

FLASH擦除、写入是由时序发生器控制的,所以擦除、写入之前需要设定合适的时钟频率(查看用户指南可知,频率必须在257KHz~476KHz),而时钟频率由选择哪种时钟源FSSELx及分频系数FNx决定(在FLASH控制寄存器2),FCL2示意图如下(FCL2默认值是0x9642,即只读、MCLK、3分频):

图7 FCL2示意图

假设选择默认MCLK作为FLASH时序发生器,默认MCLK时钟频率典型值是1.1MHz,即1126.4KHz,需要3分频(375.5KHz,此时FN1为1)或者4分频(281.6KHz,此时FN1、FN0为1)才能符合257KHz~476KHz。通过设置FN0~FN5可以将时钟分频1~64,即32*FN5 + 16*FN4 + 8*FN3 + 4*FN2 + 2*FN1 + FN0 + 1。(此处FNx是指第x位,与下文不同)如果选择3分频,设置FCTL2如下:

FCTL2 = FWKEY + FSSEL_2 + FN1; /*FN1=0x0002,此时是3分频*/

FWKEY、FSSEL_2、FNx在io430G2231.h定义,如下:

#define FWKEY (0xA500u) /* Flash key for write */

#define FSSEL_0 (0x0000u) /* Flash clock select: 0 - ACLK */

#define FSSEL_1 (0x0040u) /* Flash clock select: 1 - MCLK */

#define FSSEL_2 (0x0080u) /* Flash clock select: 2 - SMCLK */

#define FSSEL_3 (0x00C0u) /* Flash clock select: 3 - SMCLK */

/* Divide Flash clock by 1 to 64 using FN0 to FN5 according to: */

/* 32*FN5 + 16*FN4 + 8*FN3 + 4*FN2 + 2*FN1 + FN0 + 1 */

enum

{

FN0 = 0x0001,

FN1 = 0x0002,

FN2 = 0x0004,

FN3 = 0x0008,

FN4 = 0x0010,

FN5 = 0x0020,

FSSEL0 = 0x0040,

FSSEL1 = 0x0080

};

- μC/OS-Ⅱ在MSP430F149上的移植(03-01)

- MSP430与I2C总线接口技术的研究(06-14)

- 基于MSP430单片机的超声波倒车雷达监测报警系统设计(08-14)

- 2010年中国(成都)电子展胜利闭幕(08-15)

- 基于MSP430单片机的电子汽车限速器的研究(08-20)

- 基于MSP430的微功耗数据采集系统的开发应用(10-16)