基于FPGA实现的PCI-I2S接口转换电路

MPCI32用于FPGA上PCI接口的开发。

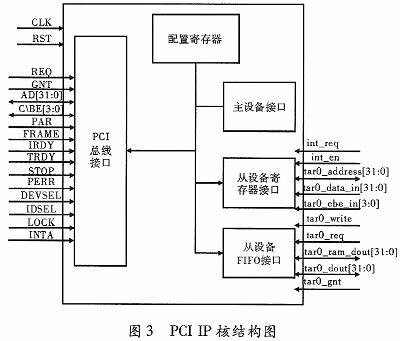

Mentor公司的PCI核完全符合PCI2.2的标准,支持33/66 MHz、32位数据的传输,PCI核的结构如图3所示,该PCI核的功能是将入口测复杂的PCI接口信号转为出口侧较为操作的用户信号。PCI核内用户侧设置有主控制接口和从控制接口以及配置寄存器等模块,其中从控制接口分为寄存器接口与FIFO接口。因为本文中仅使用了从控制接口,所以图中仅对从控制接口的信号展示。可以看出,IP核左侧的信号为PCI的标准信号,在使用时与前端PCI总线连接,右侧信号为本地数据信号,可以看出IP核将PCI上原本复用的地址线与数据线处理后分别接出为32位的地址线与32位数据线,并且原本总线上双向的数据线被区分为单向读信号线与写信号线。此外还有后端逻辑对寄存器的读写地址信号线与PCI访问逻辑的读写地址信号线,后端对寄存器使用时的请求信号线,寄存器被占用的标志信号线等。配置寄存器包含所有PCI配置空间的信息,其中包括表明设备信息的Device ID与Ven dor ID寄存器,以及命令寄存器,Base Address Register等主设备初始化时需要访问的信息,这些信息在PCI核生成时已经被设定,无需改动。

在设计PCI接口时,用户通过发起寄存器读写请求tarO_req,去访问后端寄存器,从寄存器交换数据,在CPU检测到都算逻辑未使用寄存器时,可发起占用请求并占用寄存器(tarO_gnt被置位),此时,PCI读写此寄存器中的数据。

3 音频接口设计

在驱动后端的音频芯片时首先需要通过I2C接口配置音频芯片的控制寄存器,此后根据音频数据不同的采样级别频率控制FPGA产生的时钟,最终音频数据从FPGA内部的FIFO中通过FPGA产生的时钟依据I2S协议标准向音频芯片传输。在FPGA中设计的音频接口包括I2C时序协议接口模块,I2S时钟控制接口模块和I2S时序协议接口模块。

3.1 I2C接口模块的设计

I2C总线是由飞利浦公司开发的串行总线,总线由两根信号线构成,其中SCLK为时钟信号线,SDA为双向数据线。I2C总线上的所有设备均可做为主设备,每个设备在总线上都有唯一的地址。

立体声音频编解码器TLV320AIC23B中,共有11个寄存器需要配置,所有寄存器为只写寄存器。这些寄存器分别控制芯片输出音频的左右耳机音量、左右功放音量、芯片电源、采样率等参数。在芯片的配置参数传输时,以I2C的数据线(SDA)在时钟线(SCLK)为高时下降沿条件作为数据的起始位,此后每当FPGA向TLV320AIC23B传输8位数据时,TLV320 AIC23B在第9个时钟时通过SDA向FPGA返回一个ACK信号。如果FPGA确认收到ACK信号则继续传输下一组数据,否则将重复传输此组数据。实际中示波器测量的传输波形如图4所示。

3.2 I2S时钟控制接口模块的设计

由于不同的音频数据有着不同的采样级别频率,所以在传输不同音频文件时,FPGA提供给TLV320AIC23B的时钟频率不同,为使不同采样频率的声音文件都能在本系统上正常播放,故在FPGA内部使用其DCM由主时钟12.288 MHz生成16 kHz和32 kHz两种采样时钟频率,接入缓冲器BUFGMUX中,并且通过在PCI的配置空间中开辟一个寄存器,寄存器的值接至BUFGMUX的选择端,这样通过配置PCI总线配置此寄存器即可根据播放音频的情况选择时钟频率。

3.3 I2S时序协议接口模块的设计

I2S时序接口模块的主时钟由FPGA内部提供,模块内通过对主时钟进行分频产生BCLK与LRCin,模块在每个LRCin的上升沿由缓存FIFO中读取一个16 bit的数据放入临时寄存器,此后在BCLK的每个上升沿依次由高至低读取寄存器中的每一位并赋值给数据线SDIN,并且在LRCIN的下降延时重复传输此数据,从而完成音频数据的I2S协议传输。

4 系统测试及结果

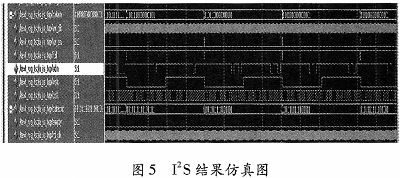

通过在上位机中向CPU内部Flash烧录一段音频数据,此后通过访问FPGA的配置寄存器将此段数据传入至FPGA内64 kB的FIFO中,后端音频模块检测到FIFO非空即开始工作。首选通过逻辑仿真软件对系统进行仿真,结果如图5所示,信号线SDIN、 LRclk,BCLK输出结果符合I2S协议规范中左对齐模式。此后可以在音频芯片模拟输出端接入耳机或功放等音频播放设备,用示波器测量其模拟输出。结果证明此系统工作正常,可以按照要求播放16 kbit·s-1与32kbit·s-1WAV音频文件。通过示波器测量的模拟输出如图6所示,可以看出明显的包络信号。通过以上结论可以看出,系统可以充分利用FPGA片内资源,从而减少对板内面积占用并减低系统功耗,也易于移植入同类的嵌入式系统中。

在本文的基础上,可以进一步发挥FPGA的灵活性,比如在开发FPGA上支持PCI从设备DMA模式,以进一步加强PCI总线的读写效率、I2

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)

- 基于DSP与PC机的PCI总线高速数据传输 (07-08)