基于PCIe总线的多路复用DMA高速传输系统的设计

库函数PlxPci_Device Find找到NT设备和DMA设备(只在主机端有),并获得设备描述符。使用PlxPci_PciBarMap函数将NTBar0、DMA Bar0(只在主机端有)和NT Bar2~NT Bar5映射到用户虚地址空间。使用PlxPci_PhysicalMap函数申请128个大小为4MB的物理内存并将其映射到用户虚地址空间作为DMA数据缓冲区使用。这些寄存器的作用如表1所示。

3.2.2 DMA管理模块

使用规定传输系统最多允许建立128对传输通道,而PEX8619芯片上只有4个DMA通道。面对128路虚拟传输通道和4路DMA物理通道的不匹配,系统中使用分时复用DMA通道的方法解决这一矛盾。

首先,分时复用要解决共享内存资源的分配,DMA数据缓冲区大小为128x4MB。为达到资源利用最大化及公平性,每一次虚拟传输通道的建立与断开都要为现存的每一路传输通道重新计算和分配DMA数据缓冲区。每一路传输通道可用于接收或发送数据的缓冲区大小计算公式为:128×4/channel total×1/2,其中channel_total为总通道数。

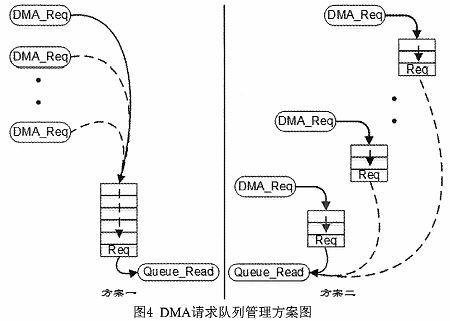

其次,需要解决DMA通道的使用分配。在多线程机制下对DMA通道请求队列的管理有2种方案,队列管理方案如图4所示。

在方案一中,每个虚拟通道的线程把自己的DMA请求(DMA_Req)放入DMA请求队列(DAM_Queue)中,Oueue Read负责从队列中取出DMA请求。在此使用锁机制,将队列写操作作为临界区,在锁定的临界区只允许让一个线程访问,其它线程排队等待。这样的方案设计简单易懂好管理,然而在实际的测试中,由于线程资源及调度是由操作系统来完成的,测试结果表明各个通道的DMA_Req并不能公平地写入队列,DMA物理通道并不能公平的服务于每一路虚拟通道,导致了各个通道间传输速率不均衡。

在方案二中,各个虚拟通道把自己的DMAReq写入自己的DMA_Queue中,Queue_Read通过轮询的方式读取各个DMA_Queue的DMA 请求,测试结果表明DMA物理通道资源能被公平的分配且请求处理效率更高。因此传输系统的DMA请求队列管理采用方案二实现。

3.2.3 系统通信模块

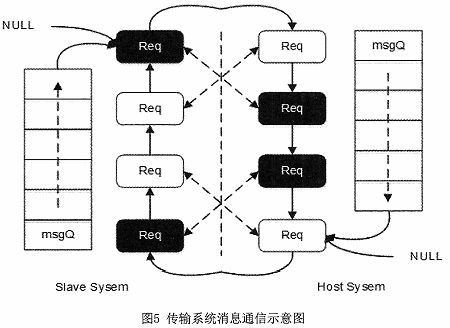

主机与从机两个处理器系统天然的分离特性,使得性能与正确性产生矛盾,如果两端的消息通信只是简单的发送/接收和处理,不能保证两端不同时使用同一资源。因此为传输系统规定了一个有顺序语义的通信机制如图5所示。

图5中黑色箭头表示的是程序的执行顺序,白色部分代表了对主机端消息的处理,黑色部分代表了对从机端消息的处理。主从机端皆有一个消息队列,所有需要发送的消息(msgQ)都先存入消息队列中,主机和从机端通过令牌机制来轮流向对方递送消息。如果一方消息队列为空,也需要让度令牌,使得对方能继续递送消息。以主机机端为例,其消息处理过程如下:(1)等待从机端发送让度令牌的消息Ack;(2)收到Ack后接收从机端的发送的消息Req;(3)对消息进行处理并且准备要发送给对方的Ack和从消息队列中取出msgQ(若消息队列为空,则填入NULL);(4)向对方发送Ack和msgQ。从机端的消息处理与主机端是一一对应的。

系统中使用NT桥的8个32位的MailBox寄存器来实现主从机的消息通信,MailBox寄存器是NT桥的链路端口和虚拟端口共有的,都可见可读可写。

令牌跳跃式的消息传递机制是否会成为整个传输系统提升传输速率的瓶颈,将在下文的实验测试中给出结论。

3.2.4 客户端通信模块

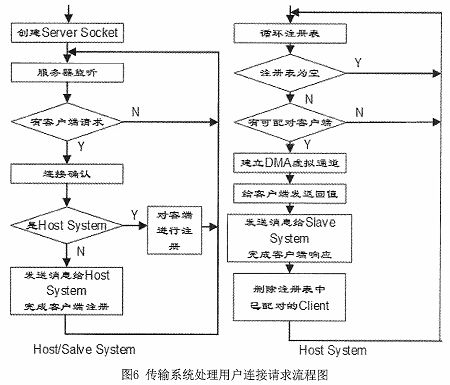

使用“Abstract”样式。为了提供一个简易通用的客户端接口,Plx_Server和Client_Register的进程间通信使用Socket实现。传输系统的主程序Plx_Server通过创建服务器(Server Socket)未向连接服务器的客户端(Client Register)提供服务。服务包括了数据收发请求,连接建立/端开请求等。Plx_Server处理Client_Register连接请求的流程如图6所示。

在图6中客户端的连接注册、客户端配对和建立传输通道都是由主机端完成的,从机端的连接注册需要交付给主机端来完成。

3.2.5 客户端API

调用客户端API(Client_Register)完成连接配对请求后,Client_Register将返回一个Socket描述符。用户只需要参考标准Socket编程规范,即可使用Socket标准函数接口,比如read、write、close等进行数据通信。

4 系统性能优化分析

为满足视频转码设备对数据传输性能的要求,传输系统除了要满足传输速率、速率均衡的要求外,CPU资源使用率也要作为考虑的因素。在测试中当处理器系统的 CPU使用率超过50%后,传输系统的总带宽随之下降。为此,传输系统做了以下优化:(1)设置Plx_Server的CPU相关性,使进程同时关联多个 CPU;(2)线程在等待或空闲时适当挂起以释放占用的CPU资源。

5 实验结果分析

本传输系统结合视频转码

- STM32 八路AD转换用DMA传输调试成功,DMA传输不错位(11-23)

- 视频并行处理系统分析与设计(08-06)

- 一种具有主从自适应功能的CPCI通用处理模块设计(01-18)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)