ADI:16位10 MSPS ADC AD7626的单端转差分高速驱动

电路特点

16位10MSPS PulSAR ADC

经过优化的单端至差分驱动器

输入为2.4MHz时,SNR为88dB

电路功能

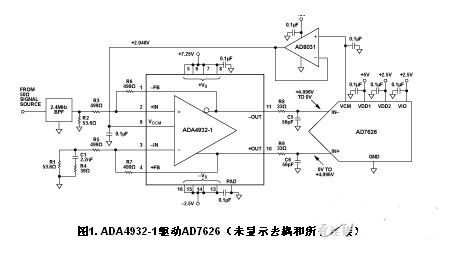

图1所示电路可将高频单端输入信号转换为平衡差分信号,用于驱动16位10 MSPS PulSAR® ADC AD7626。该电路采用低功耗差分放大器ADA4932-1 来驱动ADC,最大限度提升AD7626的高频输入信号音性能。此器件组合的真正优势在于低功耗、高性能。

AD7626具有突破业界标准的动态性能,在10 MSPS下信噪比为91.5 dB,实现16位INL性能,无延迟,LVDS接口,功耗仅有136 mW。AD7626使用SAR架构,主要特性是能够以10 MSPS无延迟采样,不会发生流水线式ADC常有的“流水线延迟”,同时具备出色的线性度。

ADA4932-1具有低失真(10 MHz时100 dB SFDR)、快速建立时间(9 ns达到0.1%)、高带宽(560 MHz,-3 dB,G = 1)和低电流(9.6 mA)等特性,是驱动AD7626的理想选择。它还能轻松设定所需的输出共模电压。

该组合提供了业界领先的动态性能并减小了电路板面积:AD7626采用5 mm × 5mm、32引脚LFCSP封装,ADA4932 -1采用3mm× 3mm、16引脚LFCSP封装),AD8031 采用5引脚SOT23封装。

电路描述

采用差分放大器成功驱动ADC需要正确平衡差分放大器的各端。

图1显示了ADA4932-1、AD7626和相关电路的原理图。在使用的测试电路中,信号源之后配置有2.4 MHz带通滤波器。该带通滤波器能抑制2.4 MHz信号的谐波,并确保只有目标频率的信号能够通过并由ADA4932-1和AD7626进行处理。

本例中信号源的特性阻抗为50 Ω,通过带通滤波器交流耦合到ADA4932-1。将信号源施加于ADA4932-1的正输入时,要求信号源也以50 Ω正确端接(通常情况下任何源阻抗均可)。选中端接电阻R2,以使R2与ADA4932-1输入阻抗的并联组合等于50 Ω。

为使ADA4932-1的两个输入端保持适当平衡和对称,与输入源阻抗等效的戴维南阻抗和端阻抗必须添加到反相输入端。在这种情况下,就涉及到滤波器的交流特性。

如图1所示,戴维南等效网络显示在ADA4932-1的反相输入端。频率为2.4 MHz时,此电路性能得到优化。C1和R4串联组合后,与电阻R1并联。频率为2.4 MHz时,C1和R4的复合串联组合等于55.6 Ω。与R1并联的55.6 Ω阻抗与戴维南等效电路在同相输入端的输入阻抗只有几欧姆之差。两个输入的匹配可确保输出对称、均衡且经过优化,可实现最低失真。

有关单端输入端接方法的详细说明,请参阅应用笔记AN-1026“高速差分ADC驱动器设计考虑”。此外,ADI公司DiffAmpCalcuator™设计工具大大简化了这一操作,并针对与差分放大器设计有关的其他问题提供了独到见解。

ADA4932-1差分驱动器的增益配置约为1(单端输入至差分输出)。由于50 Ω信号源以及在ADA4932-1输入端匹配的端阻抗的作用,相对于戴维南等效信号源电压,通道的净总增益大约为0.5。

使用配置为单位增益缓冲器的AD8031来缓冲AD7626的VCM输出电压(标称+2.048 V),即可设定ADA4932-1输出的共模电压。AD8031为ADA4932-1 VOCM引脚提供低源阻抗,并能驱动大型旁路电容,如图1所示。

当驱动AD7626(带开关电容输入的10 MSPS ADC)的高频输入时,ADA4932-1的作用尤其显著。ADA4932-1和AD7626 的IN+和IN-引脚之间的电阻(R8、R9)和电容(C5、C6)电路可充当低通噪声滤波器。该滤波器限制了AD7626的输入带宽,但其主要功能是优化驱动放大器和AD7626之间的接口。串联电阻将驱动放大器与ADC开关电容器前端的高频开关尖峰隔离。AD7626数据手册显示了20 Ω和56 pF的值。在图1所示电路中,这些值根据实际应用优化为33 Ω和56 pF。若要针对转换中的电路和输入频率对电阻-电容组合进行略微优化,只需改变R-C组合即可。但是切记,若组合不当,将限制AD7626的总谐波失真(THD)和线性度性能。此外,ADC带宽的增加会引起更多噪声。

ADA4932-1电源电压的选择也得到了优化。在电路中,对应于4.096V的内部基准电压,AD7626的输出共模电压(VCM引脚)为 2.048 V,每个输入(IN+、IN-)在0 V和+4.096 V之间摆幅,发生180°错相,这提供了ADC的8.2 V满量程差分输入。对于线性运算的每个电源电压,ADA4932-1输出级需要大约1.4 V的裕量。当电源电压关于共模电压大致对称时,能获得最佳失真性能。如果选定-2.5 V负电源,则至少需要大约+6.5 V正电源才能关于2.048V共模电压对称。

实验表明,+7.25 V正电源可为2.4 MHz信号音提供最佳的总失真性能。

使用低抖动时钟源和AD7626的单音-1 dBFS幅度2.402 MHz输入,可产生图2所示的FFT结果:信噪比为88.4

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)