基于ARM7的高精度频率计的设计

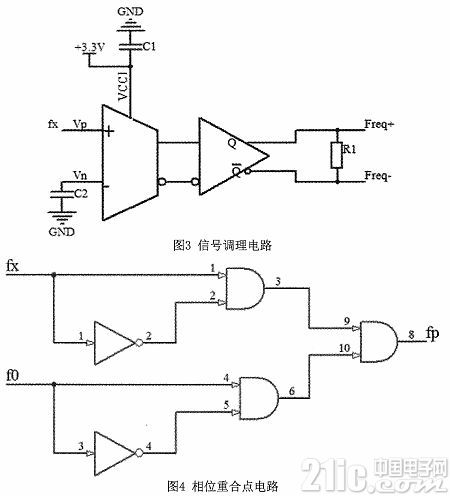

面决定采用LVDS差分信号输出来实现。电路图如图3所示。其中Vp端接被测信号,Vn端接地,当fx大于0时,Q端输出为高电平,当fx小于0时,Q端输出为低电平。

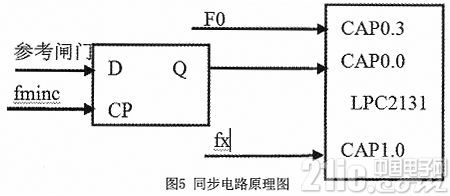

相位重合点电路的设计是整个设计中最主要的部分,其电路图如图4所示。

为了得到与f0和fx相同频率的脉冲,需要将f0和fx和本身取反延时后相与得到。最后再将两个脉冲相与得到相位重合点的频率fp。

在主控芯片中,本文选用了由PHILIPS公司生产的基于ARM7TDMI—S内核的32位微处理器LPC2131。由于本文设计的高精度频率计的实际需要,需要尽可能减小测量误差,因此低功耗就成为选择芯片的主要指标。本芯片采用冯诺依曼结构,具有高性能和低功耗的特性,ARM7TDMI—S还使用了3级流水线技术,通常在执行一条指令时,就对第二条指令进行译码并同时对第三条指令进行提取。这极大地提高了测量速度,使高精度测量能够更加快速和准确。其中LPC2131产生的PWM脉冲作为参考闸门信号。与此同时,为了保证电路的稳定性和降低成本,精简了核心电路的组成,此方案利用ARM控制芯片LPC2131中两个32位可编程定时/计数器。LPC2131通过片内PLL可实现60MHz的CPU工作频率,不仅满足设计要求,降低了成本,而且提高了运算速度,避免引入不必要的误差。

由图2可知,fp与参考闸门信号共同决定实际闸门的开闭。实际闸门与标准频率和被测频率同步的原理如下:fp接在D触发器的CP端,参考闸门信号接在D端,每当CP端接收到一个脉冲,就对参考闸门信号进行采样。其中Q端与LPC2131相连来控制LPC2131中两个计数器同时计数。如果参考闸门信号为低电平,那么Q端就为低电平,计数器不计数,如果参考闸门信号为高电平,那么Q端就为高电平,计数器开始计数,这样实际闸门就与标准信号和被测信号达到了同步。原理图如图5所示。

3 软件设计

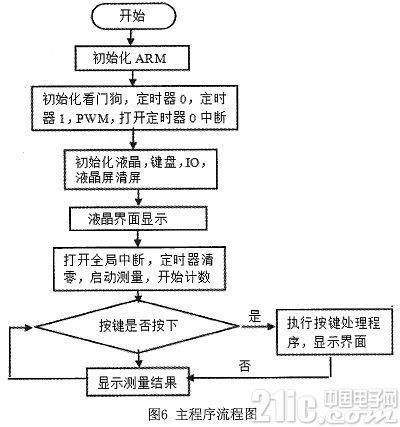

本文所设计的系统其软件是在ADS1.2平台上用C语言编写完成的。并使用EasyJTAG仿真器进行仿真。LPC2131在频率计中一方面要将计数器的计数N0和Nx经过公式(2)算出被测频率值,并显示在LCD上,同时还负责外部面板的按键功能。图6为系统主程序流程图。

4 结束语

本文选用32位ARM7的芯片作为核心的主控芯片,并利用相位重合检测技术对高精度的频率计进行了设计,为了让实际闸门开闭时间与标准频率和被测频率同步,采用了对标准频率和被测频率的相位重合点的捕捉,有效地消除了±1个字的计数误差,提高了测量准确度;由于使用了32位ARM7的芯片比过去使用16位单片机设计提高了控制系统和测量数据处理的速度。相位重合点生成电路是这种测量频率方法的关键电路,使用简单的逻辑电路进行设计,降低了整体电路的成本;同时使用恒温晶振作为标准频率的产生装置,使本系统的测量频率误差能够达到10-10量级。

- 基于DSP的高精度数字频率计的设计(02-03)

- 基于TMS320F2812的数字频率计的设计(05-11)

- 基于AT89C51单片机的量程自切换频率计(01-25)

- 基于FPGA自适应数字频率计的设计(08-14)

- 硬件描述语言Verilog HDL设计进阶之:自动转换量程频率计控制器(06-05)

- FPGA设计频率计算方法(06-04)