基于DSP的1553B总线接口电路设计

机载火控数据采集技术需要满足实时采集、实时传输、实时存储以及方便下载的需求,以便于地面人员对获取信息的处理。这样可以更好的动态掌握飞机的作战状态,提高飞行训练效果和作战能力。1553B数据总线作为航空电子综合系统中信息交流的主干道,使机载数据能在复杂的环境中得以保存、交换。DSP作为高速性能的数据处理芯片,可以实现较高速率的数据采集。FPGA作为高速、复杂的组合逻辑和时序逻辑控制器件,更适合外围电路的连接,将两者组合使用,满足了数据的高速传输与存储。同时,随着1553B数据总线协议标准的颁布,许多电器件公司开发了能将1553B数据总线与CPU相连接的相应接口芯片。这样,使得数据在传输过程中更加稳定、高速、可靠。本文旨在探讨采用DSP与相应接口芯片BU-61864,设计相关电路来实现机载火控数据的采集。

1 1553B数据总线

MIL_STD_1553B是军工定义的数字时分制命令/响应式多路传输数据总线,采用曼彻斯特Ⅱ编码,半双工工作方式,数据传输的速率为1Mbps,能挂接31个远置终端,支持3种终端类型。该标准作为美国国防部武器系统集成和标准化管理的基础之一,被广泛应用于飞机综合航电系统、外挂物管理与集成系统,并逐步扩展到飞行控制等系统及坦克、舰船、航天等领域。我国参照MIL_STD_1553B标准,于1987年颁布了相应的军用标准,即GJB-289A。

MIL_STD_1553B定义了连接在总线上的3种类型终端,即总线控制器(BC)、远程终端(RT)和总线监视器(BM)。

1)总线控制器(Bus Controller简称BC):总线控制器的功能就是控制总线上的数据流收发,数据总线上有很多BC,但是每次只能一个BC工作。而且一些RT也能担任BC的工作。BC发送命令给RT,接收并确认命令之后,RT给出响应。

2)远程终端(Remote Terminal简称RT):RT是一个采用1553B数据总线连接各式各样子系统的设备,RT接收BC传送的命令、检测错误并且反馈错误,即要对BC作出响应。

RT特征如下:

①一条数据总线可以连接多达31个RT。

②每一个RT可以有多达31个子RT。

③RT只有当接收并确认BC的命令之后,才会作出响应,属于被动式。

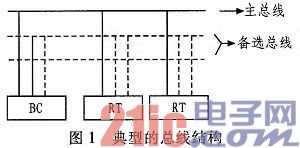

3)总线监控(Bus Monitor简称BM):BM监听总线上的所有数据传输并且记录指定的消息。他们的连接如图1所示。

1553总线上的数据是以串行数字脉冲编码调制的格式进行传输,采用的是曼彻斯特Ⅱ双相电平码作为数据的编码格式。逻辑1电平由I/O编码组成(即一个正脉冲后面紧跟着一个负脉冲),逻辑0由0/1编码组成(即一个负脉冲后面紧跟着一个正脉冲)。

1553B总线上的信息是以字的形式传输的。包括一个3位的同步位、16位信息位以及一位奇偶校验位。总线上的字共有3种类型:命令字、数据字、状态字。他们的具体格式如图2所示。

2 硬件选择

2.1 TMS320C6713芯片介绍

DSP芯片选用TI公司生产的TMS320C6713,该芯片为TMS320C6000系列DSP平台上产生的新的浮点型芯片。其有225 MHz的高速运行速度,提供13.5亿次/秒浮点运算,18亿/秒的指令操作。而且,C6713使用2级缓存的架构以及强大多样化的外设集:1级程序缓存是一个4 kB的直接映射高速缓存,1级数据高速缓存是一个4 kB的2路组相联高速缓存。2级内存和缓存有一个256 kB的存储空间,在程序和数据之间共享。这个256 kB存储器中64 kB可以配置为寄存器、高速缓存或者两个的组合,192 kB作为对应的SRAM。可见,C6713应用非常灵活。外设集包括2个多通道缓冲串行端口(McBSPs),2个内部集成电路(I2C)总线,一个专用通用输出/输出(GPIO)模块。2个通用定时器,主机接口(HPI),以及1个能够与SDRAM、SBSRAM、异步外设无缝连接的外部存储器接口(EMIF),增强型直接内存访问(EDMA)控制器(16个独立通道)。

C6713有着非常好的运算能力、高效的指令集、智能外设、大容量的片内存储器和大范围的寻址能力。因此,更适合用于对运算能力和存储量有较高要求的场合。

2.2 BU-61864芯片介绍

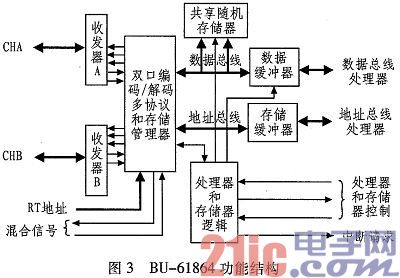

由于本文选用的DSP芯片C6713的I/O电平为3.3 V,为简化硬件电路设计,选用DDC公司的全3.3 V的1553B协议芯片BU-61864,这样无需电平转换,大大提高设计效率和减少相关工作器件。BU-61864芯片内部集成了双收发器、编/解码器、协议逻辑、内存管理和中断控制逻辑,支持BC/RT/MT模式,还提供了一个4kB的内部共享静态RAM和与处理器总线之间的缓冲接口,并且有可扩展的4K*17bitRAM,两个1553B收发器芯片。

BU-61864有灵活的接收/存储器接口,能完全实现1553B协议所规定的消息传输外,还具有较强的消息管理能力,能全面兼容1553B协议。其功能结构框图如图3所示。

3 硬件接口电路设计

本系统由DSP主导,

1553B DSP BU-61864 机载火控数据 相关文章:

- 基于DSP的1553B总线系统设计与实现(10-08)

- 基于μC/OS-Ⅱ的1553B和ARINC429总线实时协议转换系统的设计(08-09)

- FPGA/DSP技术的1553B飞机总线系统通讯软件的设计(01-15)

- 基于LXI总线的1553B通讯模块设计与开发(11-24)

- 基于1553B总线的航天大功率电动舵机控制器设计(12-21)

- 基于FPGA的1553B总线接口设计(12-20)