基于MPC8280的PCI驱动设计

摘要 芯片MPC8280的主频最高为450 MHz,仅靠运行在其上的软件虽可实现路由交换功能,但交换容量仅约为40 Mbit·s-1,无法满足多路千兆交换性能要求。利用MPC8280的PCI口外接千兆交换芯片BCM56514,能突破这一性能瓶颈。基于MPC8280的PCI驱动,使得MPC8280通过PCI却婵占涠列床僮鳌⑴渲每占涠列床僮骱I/O空间的读写操作,并实现对BCM56514的配置、控制及路由表的更新,从而使MPC8280在路由交换领域得以应用。

近年来,多媒体通信技术应用迅猛发展,对网速的要求也迅速提升。为适应这一趋势,与网络相关的终端设备和路由交换设备的性能均亟需提升。在当今中国,计算机作为网络终端设备,网口的标配速率已由100 Mbit·s-1改为1 000 Mbit·s-1,交换机、路由器等作为路由交换设备,交换容量量级也由原来100 Mbit·s-1上升到1 000 Mbit·s-1甚至10 Gbit·s-1。MPC8280是由Freescale公司推出的双地址总线双处理器芯片,自其推出以来,因其丰富的外围接口已在航空航天、通信电子、医疗器械、交通设施等领域得到广泛应用,然而在今日迫切需求的大容量路由交换领域,却因其最高主频为450 MHz的限制,依靠运行在MPC8280上的软件扣除中断处理、系统管理等开销外,实现的交换容量仅为40 Mbit·s-1,在多路千兆交换应用中存在性能瓶颈。利用MPC8280的PCI口外接千兆交换芯片BCM56514,使得运行在MPC8280上的软件仅作路由计算和路由表的维护,而将交换控制交由BCM56514实现,可突破性能瓶颈。完成PCI驱动设计是这一方法能得以实施的先决条件,MPC8280通过PCI内存空间读写操作、配置空间读写操作和I/O空间读写操作,实现对交换芯片的配置、控制及路由表的更新,从而使MPC 8280在大容量路由交换领域得到成熟应用。

1 PCI知识介绍

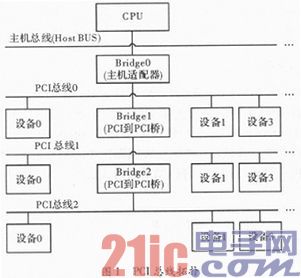

PCI为Peripheral Component Interconnect的缩写,是一种总线规范,用于外围设备互联。目前使用2.2版本的PCI规范。主要由时钟信号(PCI_CLK)、控制信号 (FRAME、IRDY、DEVSEL、TRADY、STOP、IDSEL)、地址数据复用信号AD[31:0]及校验和错误指示信号(SERR、PERR)构成。地址和数据信号可扩展到64 bit,时钟信号常用33 MHz,可扩展到66 MHz,速率可达528 MByte/s。采用分段分层结构,其总线拓扑结构如图1所示。

2 PCI驱动设计

PCI驱动通过配置寄存器,完成总线初始化,并提供PCI配置空间读写、PCI内存空间读写、PCI I/O空间读写和中断函数接口。上层应用利用这些操作接口发现外部交换芯片,并能获取交换芯片信息,实现对外接交换芯片的配置管理、路由表更新、状态回读等操作,最终实现PCI驱动设计。

2.1 PCI驱动流程设计

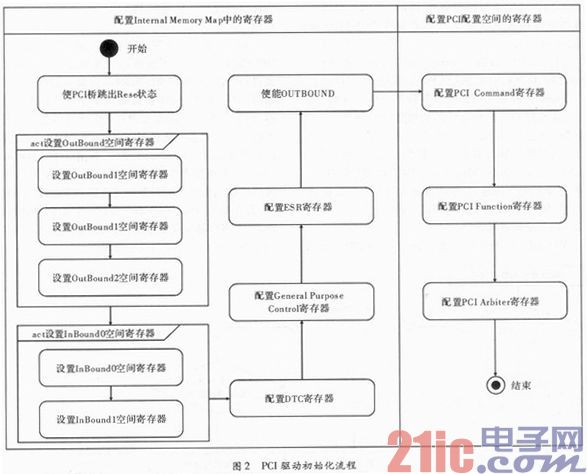

首先通过设置寄存器,使芯片跳出PCI重启状态,接着根据系统的地址分配对Outbound和Inbound寄存器组进行配置,然后对PCI使用的字节序、错误状态和Master模式进行配置,最后使能PCI内存空间读写和配置空间读写。使用UML的活动图对PCI驱动流程设计建模如图2所示。

2.2 配置空间读写设计

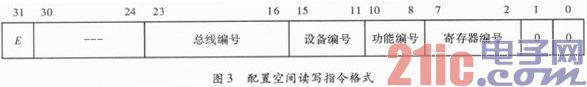

指令按照一定的数据格式优先写到CONFIG_ADDR寄存器,然后通过向CONFIG_DATA寄存器填入数据,完成写操作,或从CONFIG_DATA读出数据,完成读操作。无论CONFIG_ADDR寄存器的数据是否需要改变,每次操作都必须先对CONFIC_ADDR寄存器操作,然后才可对CONFIC_DATA寄存器操作,否则操作无效。指令数据格式如图3所示。

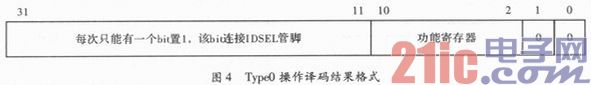

配置空间操作时,地址译码过程如下:例如Device Number为0b01011时,对应的十进制数为11,则Bit[31:11]中的Bit11置1,其他Bit为0,此时在硬件上将IDSEL信号连接到Bit11的PCI设备将被选中;若Device Number为0b01100时,对应的十进制数为12,则Bit[31:11]中的Bit12置1,其他Bit为0,此时在硬件上将IDSEL信号连接到Bit12的PCI设备将被选中;Device Number的特殊定义如下;0b01010将选定Bit[31];0b11111将执行特别操作;0b00000将对PCI桥自身进行操作。译码结果的格式如图4所示。

共有两种操作类型:了ype 0操作和Type1操作。Type0操作适用于目标设备和PCI桥在同一总线上,PCI桥直接根据从上层总线接收到指令中的Device Number进行地址译码,并将Bit[31:11]数据中对应的Bit置1,Bit[1:0]设置成0x00,在PCI总线配置操作的地址时段,将译码结果发送到PCI总线的AD[31:0]上。

Type1操作适用于目标设备和PCI桥不在同一总线上,需经过PCI桥将完整的数据继续向下传递。当PCI桥在配置空间操作的地址时隙从AD[31:0]收到指令时,判断目标设备是否在其负责的范围内,若不在,将不处理。若在,则将AD[31:0]的

MPC8280 PCI 驱动设计 内存空间读写 配置空间读写 I/O空间读写 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)