一种智能化ARINC429通讯卡设计与实现

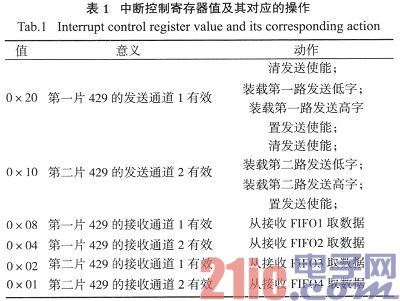

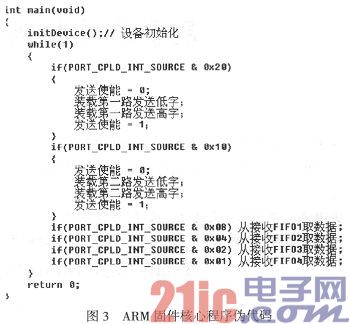

处理器到ARINC429接口芯片,故负责地址总线电压转换的两片SN74LVC4245-DBL芯片DIR引脚可以接死;而负责双向数据总线电压转换的两片SN74LVC4245-DBL芯片DIR脚则需要通过CPLD进行逻辑控制。 2.2 DEI1016/BD429与CPLD的接口逻辑设计 ARINC429通讯卡片选由LPC3250的CS1和地址BA11~BA4共同控制,即当CS1有效且BA(11 to 4)=“00000000”时选通,全译码,地址空间为E100 0000-E100000F 1)数据发送逻辑设计 DEI1016是16位数据线,所以32位数据字必须分成两个16位写入,而控制字只需一次写入即可。以下VHDL代码实现了对429数据发送的控制: LD_1(0)=‘0’WHEN WR=‘0’AND A=X“4”ELSE‘1’;--第1片429发送低字 LD_1(1)=‘0’WHEN WR=‘0’AND A=X“5”ELSE‘1’;--第1片429发送高字 LDCW_1=‘0’WHEN WR=‘0’AND A=X“6”ELSE‘1’;--装载控制字 ENTX_1=‘0’WHEN WR=‘0’AND (A=X“0”OR A=X“1”)ELSE‘1’;--置使能发送有效 2)数据接收逻辑设计 本通信系统实现两发四收,4个接收通道接收到的数据放在各自独立的FIFO中。数据接收采用中断-查询方式实现,即由接口芯片DEI1016的DR信号有效产生中断,通知处理器有新的有效数据到达。由于四路接收通道共用一个中断,所以必须在CPLD逻辑中实现中断屏蔽,并在中断有效时可查询是哪一路接收通道引发的中断,对于中断的处理逻辑为 INT=RDY_429_1(0)AND RDY_429_1(1)AND RDY_429_2(0)AND RDY_429_2(1);--中断信号处理 以上逻辑表明,4个接收通道中任一路有数据时都会引发中断,此时查询数据线,即可得出是哪一路接收引发的中断。 3 ARM固件程序设计 同件程序担任着通讯系统最基础最底层的工作,是硬件设备的灵魂,且由于硬件设备除了固件以外没有其它软件组成,所以固件也就决定着硬件设备的功能及性能。本系统中ARM固件中断源为一个六位的寄存器,高位到低位分别标志:第一路发送、第二路发送、第一片两路接收、第二片两路接收路接收。 在本系统中,ARM固件程序需循环装载控制字,然后检查中断控制寄存器(PORT_CPLD_INT_SOURCE)的值,根据该值做具体的发送和接收操作。中断控制寄存器的取值及其对应的操作在表1中给出。 根据以上的分析阐述,给出程序的伪代码如图3所示。 4 结束语 ARINC429是航空电子系统中应用广泛的通信标准,而ARM微处理器在目前的测控领域也占有相当重要的位置,因此基于ARM微处理器的ARINC429通信系统无疑有着很好的适用范围和实用意义。同时,上述设计的接口通信板在多个不同的航空电子系统中成功的应用,证明了其正确性和高效性。

AKM APINC429 LPC3250 DEI1016/BD429 相关文章:

- 基于WinCE6.0的LPC3250串口驱动程序开发(01-05)

- 一款基于LPC3250单片机的智能电子血压计设计(08-19)

- 基于USB接口的ARM9微控制器外部存储器下载工具— MOLY-DO(02-18)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)