基于SPB的嵌入式音频处理系统设计

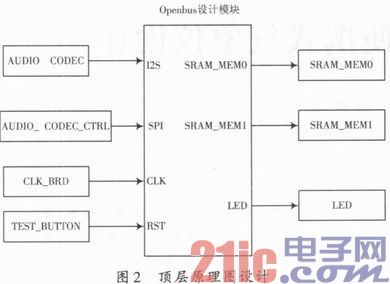

顶层原理图通过约束文件,将下载到FPGA中的嵌入式系统设计与FPGA器件的物理管脚连接起来。顶层原理图设计中,音频流控制器I2S与音频编解码器(AUDIO_CODEC)相连,SPI控制器与音频编解码器控制器CS4270(AUDIO_CODEC_CTRL)相连,如图2所示。

2.2 软件平台文件设计

在SPB基础上搭建访问NB 3000开发板的音频接口,并对音频流数据进行处理的软件平台文件(SwPlatform),如图3所示。

NB 3000开发板上的音频编解码器为CS4270,因此图3中选择CS4270 Audio Codec Driver模块,不需要再自行编写音频编解码器的驱动代码。设计采用SPI作为配置和控制,I2S用来传输数字音频数据流。因此软件平台文件的底层设计选择了I2S Master Controller和SPI Master Controller模块。中间层设计选择了I2SDriver、SPI Driver和CS4270 Audio Codec模块。软件平台文件使硬件外围设备的访问变得容易,底层模块为特定的外围设备提供了配置数据和驱动代码。设计软件平台文件时,选择什么样的模块,取决于设计中需要访问哪些外围设备。

2.3 嵌入式代码设计

FPGA嵌入式系统设计中,嵌入式工程是“嵌在”微处理器中的。嵌入式代码就是在软件平台构建器上搭建的软件平台的基础上完成的软件编程。嵌入式工程中的软件代码,主要完成音频数据流的获取、音频数据流的处理和将处理好的音频数据流送到NB 3000开发板的喇叭上。主要程序代码如下:

3 设计总结

将嵌入式设计文件下载到智能开发平台NanoBoard 3000上的FPGA器件后,利用音频线将电脑或者音箱的音频源送到NanoBoard 3000的音频输入接口,就能从喇叭上听到处理后的音频效果。设计过程表明,AD的软件平台构建器(SPB)为FPGA嵌入式设计访问硬件电路相关外围设备提供了底层软件驱动提供了便利。通过搭建软件平台,调用IP模块,避开了对于底层硬件的驱动程序的编写,只要掌握高级C语言就可以方便地对外围设备进行编程,简化了嵌入式代码的编写,缩短了FPGA嵌入式设计的开发时间。

- 基于多内核处理器ADSPBF561的高性能视频控制系统设计(02-16)

- G.726语音编解码在SoPC系统中(06-06)

- 基于DSP Builder的 软件无线电调制器的设计与实现(06-06)

- 采用Linux与DSP/BIOS实施双OS信号处理技术(12-21)

- 三大主流开源硬件对比:Arduino vs BeagleBone vs Raspberry Pi(10-22)

- 八款最佳Raspberry Pi 操作系统/项目(10-22)