基于ARM处理器S3C2440A的便携式视频展示台的设计

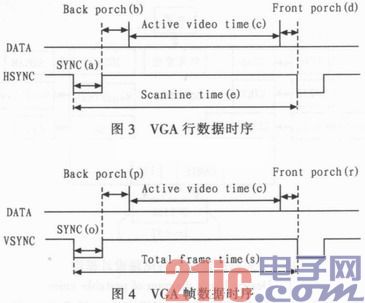

根据图3、图4所示SVGA显示时序的特点,对LCD控制器中的控制寄存器进行如下配置。

1)LCDCON1寄存

CLKVAL:确定VCLK频率的参数。公式为VCLK=HCLK/[(CLKVAL+1)x2],在本设计中S3C2440A的HCLK=100MHz,VCLK=40 MHz,故需设置CLKVAL=0.25,设置BPPMODE=0xC,即选择TFT 16位模式。

2)LCDCON2寄存器

VBPD:确定帧同步信号和帧数据传输前的时延,是帧数据传输前延迟时间和行同步时钟间隔宽度的比值,如图4所示,VBPD=p/c=0.6 ms/20 μs=30。

VFPD:确定帧数据传输完成后到下一帧同步信号到来的一段延时,是帧数据传输后延迟时间和行同步时钟间隔宽度的比值,VFPD=r/c= 0.026 ms/20μs=10。

LINEVAL:确定显示的垂直方向大小,LINEVAL=YSIZE-1=599。

VSPW:确定帧同步时钟脉冲宽度,是帧同步信号时钟宽度和行同步时钟间隔宽度的比值,VSPW=o/c=0.1 ms/20μs=5。

3)LCDCON3寄存器

HBPD:确定行同步信号和行数据传输前的延时,描述行数据传输前延迟时间内VCLK脉冲个数,HBPD=bxVCLK=2.2μsx40 MHz=88。

HOZAL:确定显示的水平方向尺寸。这里HOZAL=XSIZE-1=799。

HFPD:确定行数据传输完成后到下一行同步信号到来的一段延迟时间,描述行数据传输后延迟时间内VCLK脉冲个数,HFPD=dxVCLK=1 μsx40 MHz=40。

4)LCDCON4寄存器

HSPW:确定行同步时钟脉冲宽度。描述行同步脉冲宽度时间内VCLK脉冲个数,HSPW=axVCLK=3.2μsx40 MHz=128。

5)LCDCON5寄存器

BPP24BL:确定数据存储格式。此处设置BPP24BL=0x0,即选择小端模式存放。

FRM565:确定16位数据输出格式。设置FRM565=0x1,即选择5:6:5的输出格式。

4 结束语

文中根据市场对视频展示台的大量需求现状,提出了基于ARM9的S3C2440的便携式视频展示台的设计方案。与用CPLD/FPGA来实现VGA显示的系统相比,本方案节约成本和资源,且接口电路简单,应用灵活、可靠。由本方案做成的视频展示台体积小,易于携带。本方案经过Linux软件测试论证,方案切实可行,对实物、图片、文档或者过程的显示效果清晰,无抖动。

- ARM9 S3C2440—ADC和触摸屏控制详解(11-28)

- 四 ARM9(S3C2440)的ADC和触摸屏控制——理论知识(11-27)

- ARM9S3C2440—ADC和触摸屏控制详解(11-26)

- S3C2440+ADS1.2+H_JTAG 实现单步调试(11-25)

- S3C2440 AD转换器(11-21)

- s3c2440之ADS移植keil(11-21)