多核嵌入式系统的节能研究

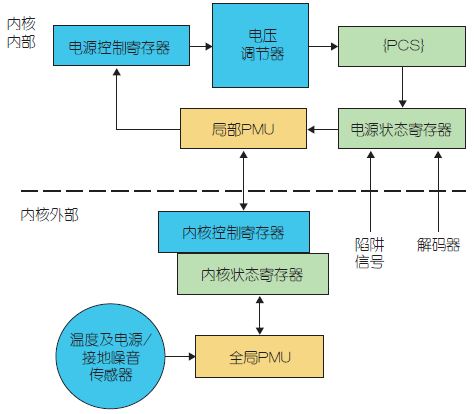

能模式。片上模拟电压调节器和时钟调节器将读取PCR中的内容,并通过读取的数据对PSC上的DVFS、电源门控、时钟门控进行控制。请注意,LPMU并不直接控制整个内核中的节能单元(如DVFS)。反之,LPMU将通过内核控制状态寄存器(CSR)向全局电源管理单元(GPMU)发送信号,CSR转而通过内核控制寄存器(CCR)实现内核级节能。内核中的电源状态寄存器通过陷阱逻辑和解码器进行更新,当需要进行特定中断服务或要对特定指令进行解码时,陷阱逻辑和解码器将会发出PSC即将激活的信号。同样,PSC也可以对自身的PSR进行更新,从而在系统长时间不工作(空闲或阻塞状态,最好在内核中对其进行局部监控)时发出即将节能的信号。

图4:自主硬件节能逻辑的架构。

图5:全局电源管理单元。

在图4中的虚线下方及内核外部是芯片级GPMU,它将会读取片上传感器上热点和电源接地噪声(它们是全局可观测现象)的数据,并为内核及其他芯片级组件做出相应的智能节能决定。GPMU通过内核状态寄存器(CSR)和内核控制寄存器(CCR)与内核及其他组件进行交互。整个内核的电源门控、时钟门控以及DVFS通过GPMU进行控制。图5展示了GPMU的交互(CR和SR分别表示控制寄存器和状态寄存器)。请注意,本文在逻辑上将所有芯片级组件都视为内核。

案例研究:英特尔迅驰中的节能

英特尔迅驰双核处理器(Core Duo)局部采用了自主电源管理方案,它是英特尔公司针对移动市场开发的首款通用芯片多处理(CMP)商用嵌入式处理器。这种内核可实现两个主要目标:首先,在平台所能承受的最高温度下实现性能的最大化;其次,电池的续航能力比前几代处理器更强。

操作系统将英特尔双核处理器视为两个独立的执行单元,但在与电源管理相关的所有操作中,平台则将整个处理器视为单一实体。英特尔选择将内核电源管理与整个CPU和平台的电源管理分开。为了实现这个目标,必须让电源及温度控制单元成为内核逻辑单元的一部分,而不是像以往那样作为芯片组的一部分。将电源及温度管理数据流迁移至处理器后,就可以采用一种允许所有内核根据自身需求请求节能状态的硬件协调机制,从而最大化单个内核的节能效果。CPU将按照两个内核请求中的最低标准确定并进入相应的节能状态,例如芯片组电源管理硬件和数据流的单一CPU实体。由此,软件可以按照ACPI协议对每个内核单独进行管理,而实际的电源管理则遵守平台和CPU的共享资源限制条件。多核处理器内核之间的相关性较复杂,内核对系统级参数的作用还不确定,而且ACPI电源管理协议也不是针对如此复杂的多核处理器而开发的。因此,需要开发一种新型的电源管理方案,这样的方案必须能在新兴的多核嵌入式处理器中将硬件节能逻辑和由操作系统控制的调度更好地整合到一起。

英特尔推出的双核处理器被分割成三个域。内核、各内核的一级缓存以及局部温度管理逻辑单元作为电源管理域独立运行。此外,包括二级缓存、总线接口及中断控制器在内的共享资源形成另一个电源管理域。所有域将共享同一个电源平面和同一个单核PLL,因此均在相同的频率和电平下运行。与细粒度节能方案相比,这是一个基本限制。但是,每个域都有独立的时钟分配(主干(spine))。内核的时钟分布主线单独进行门控,从而实现最基本的内核级节能方案。只有在两个内核都处在空闲状态且没有共享操作(总线操作和缓存访问)的情况下,才能对资源共享主干进行门控。若需要,即使在两个内核的时钟都停止的情况下,也可以将资源共享时钟保持在活跃状态,以便进行L2侦听和中断控制器信息分析。英特尔Core Duo技术还引入了包括L2动态调整在内的增强型电源管理特性。为了实现节能,系统必须进入更低电压的空闲状态,而为了达到这一目的,必须动态地调整/关闭L2缓存,从而为DeepC4状态做准备。

- 嵌入式应用中的能耗调试(04-17)

- DIY智能家居:基于AVR的智能节能插排的系统解决方案(04-16)

- 户外电源节能减排及艾默生CT解决方案(12-19)

- 详述声光控电路及节能照明系统的设计(12-16)

- S7-200 PLC与组态王在变频器节能项目上的应用(12-15)

- 走出变频器节能的误区(12-13)