集成PGIA、用于工业级信号的低功耗、多通道数据采集系统

电压之间的误差。

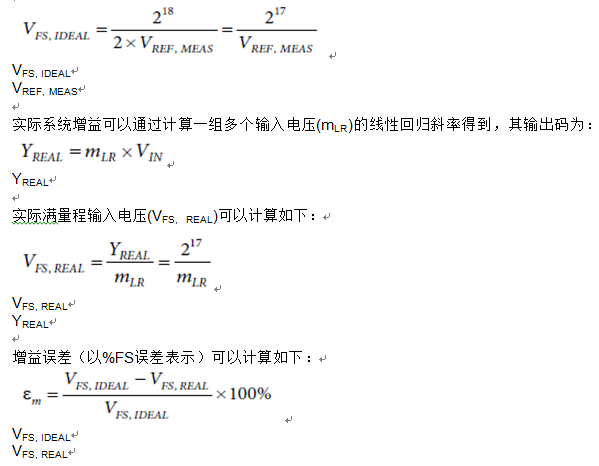

理想满量程输入电压(VFS, IDEAL)与ADC分辨率(AD7982为18位)以及基准电压(VREF)的精度成函数关系。基准电压误差会导致ADC的增益误差。为了去耦基准电压误差与ADC增益误差,使用精密万用表测量VREF。然后便可利用下式计算理想满量程输入电压:

系统增益误差随AD8251增益而变,但各通道独立。因此,增益误差针对四个增益配置分别进行测量,但在系统中仅使用ADG1207的其中一个通道。

系统噪声分析

精密数据采集系统的关键设计目标之一是实现高信噪比(SNR),这可以通过增加满量程信号幅度和/或降低系统中元件产生的噪声功率实现。

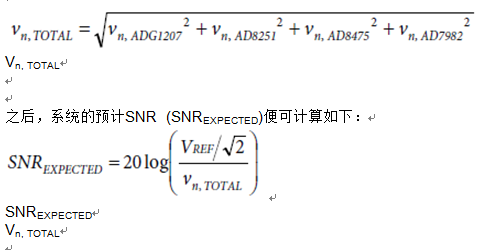

系统中的总噪声功率可以通过元件各自的噪声功率折合到AD7982输入端的和方根(rss)计算得出:

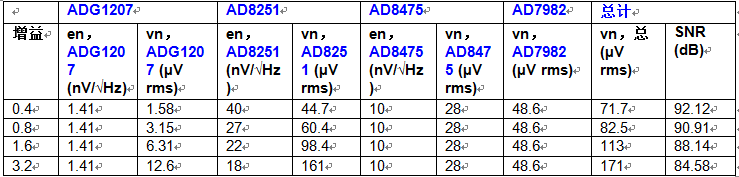

系统中各元件的预计噪声贡献以及整个系统的预计SNR性能如表2所示。在总系统噪声计算时,忽略系统中无源元件的热噪声贡献。

AD7982 ADC噪声

AD7982 ADC噪声与其固有量化噪声和内部元件(比如产生热噪声的无源元件)导致的噪声成函数关系。

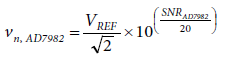

AD7982的rms输入电压噪声可以通过下式,利用其SNR额定值计算:

AD7982 (SNRAD7982)的SNR额定值约为96 dB(使用4.096 V基准电压源)。

AD7982输入端的单极点RC滤波器限制了来自上游元件的宽带噪声。较小的滤波器带宽可以通过进一步限制噪声功率而改善SNR:然而,其时间常数也必须足够短,以便建立电压反冲——这是因为AD7982输入端在采集阶段重新连接前端电路而发生电荷注入。适合系统的带宽至少为5 MHz(更多信息,请参见《模拟对话》文章:精密SAR模数转换器的前端放大器和RC滤波器设计)。

AD8475漏斗放大器噪声

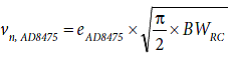

AD8475 (vn, AD8475)产生的rms噪声是其折合到输出NSD (eAD8475)以及AD7982输入端RC滤波器带宽(BWRC)的函数:

其中,eAD8475 = 10 nV/√Hz。

AD8251仪表放大器噪声

AD8251用作增益级,可通过将小幅度信号的幅度提升至更接近AD7982输入端的±VREF范围,从而改善它们的SNR。理想情况下,如果系统增益以系数G增加,则输入信号的SNR(单位:dB)将会改善:

然而,这种水平的改善实际上却是做不到的,因为宽带噪声同样为电路的噪声增益所放大。幸运的是,这种性能的下降不如信号增益导致的性能改善那么明显。

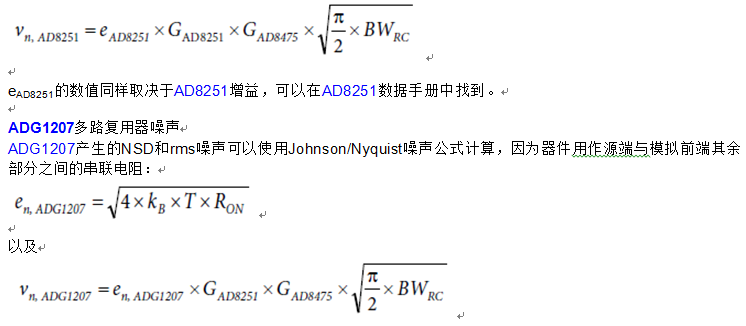

AD8251产生的rms噪声是其折合到输入NSD (eAD8251)、其增益设置(GAD8251)、AD8475的衰减系数(GAD8475)以及AD7982输入端的噪声滤波器带宽的函数。

各通道的电阻(RON)可在ADG1207数据手册中找到。

系统噪声性能的计算结果汇总如表2所示。总噪声的最大贡献因素是AD8251仪表放大器和AD7982 ADC。

表2.多通道数据采集系统的噪声性能

建立时间分析

当图1中的电路对多通道进行采样时,每一个不同的输入都由ADG1207合并至一个时分多路复用信号。多路复用信号本质上是断续的,并且通常在较短的时间间隔内具有较大的电压阶跃。对于图1中的系统而言,两个连续通道之间的差分电压在ADG1207输入端可高达20 V,而分配的建立时间仅等于采样周期。

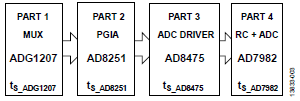

图3显示了图1中电路的建立时间模型。系统中每一个元件都有各自的建立特性(参见后文内容)。

图3.CN-0345电路建立时间模型

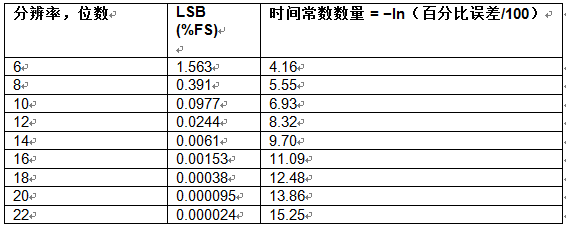

建立时间定义为模拟前端电路建立至某一精度的输入阶跃所需的时间。此精度单位通常采用百分比误差(比如0.1%或0.01%),但在转换系统中,将其与分辨率相关联也是非常有益的做法。例如,建立至16位分辨率大约等同于建立至0.001%。表3显示了单极点系统建立至百分比误差与建立至分辨率之间的关系。

表3.百分比误差和有效分辨率

估算含有多个元件的模拟前端建立时间并非易事,原因有多个。首先,很多器件都没有注明极高精度的建立时间特性。有源器件的建立时间与建立精度同样不是线性的,并且相比0.1%,建立至0.01%可能需要长达30倍时间。这有可能是因为放大器内部的长期热效应所导致。建立时间还与器件驱动的负载有关,并且通常不表征多个负载条件。

在没有特性测试平台的情况下测量高精度建立时间同样十分困难,因为存在示波器过驱和灵敏度的影响,此外生成具有足够上升时间和建立时间的输入脉冲也很困难。

分析电路时,使用某些边界与假设,可以估算出建立时间。总建立时间可以通过单个元件建立时间的和方根(rss)计算:

ADG1207建立时间

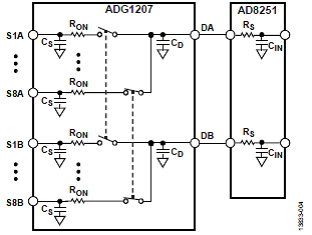

CMOS开关的等效电路可以近似看作理想开关与电阻(RON)串联连接,以及与两个电容(CS、CD)并联连接。随后,多路复用器级和相关的滤波器可以如图4所示建模。

图4.ADG1207建立时间模型

各通道工作情况类似于具有决定建立时间的相关时间常数的RC电路。动态切换通道

- 基于DSP的广播级数字音频延时器(06-07)

- 基于AD9268的短波接收全数字传输结构(07-25)

- DSP与数据转换器协同工作所必须考虑的10大因素(01-26)

- 基于ADC0809和51单片机的多路数据采集系统设计方案(10-29)

- 基于TLC320AC01与DSP的接口电路设计(01-15)

- 基于DSP和CPLD技术的多路ADC系统的设计方案(05-19)