基于ARM的CRC算法和基于FPGA的算法性能比较

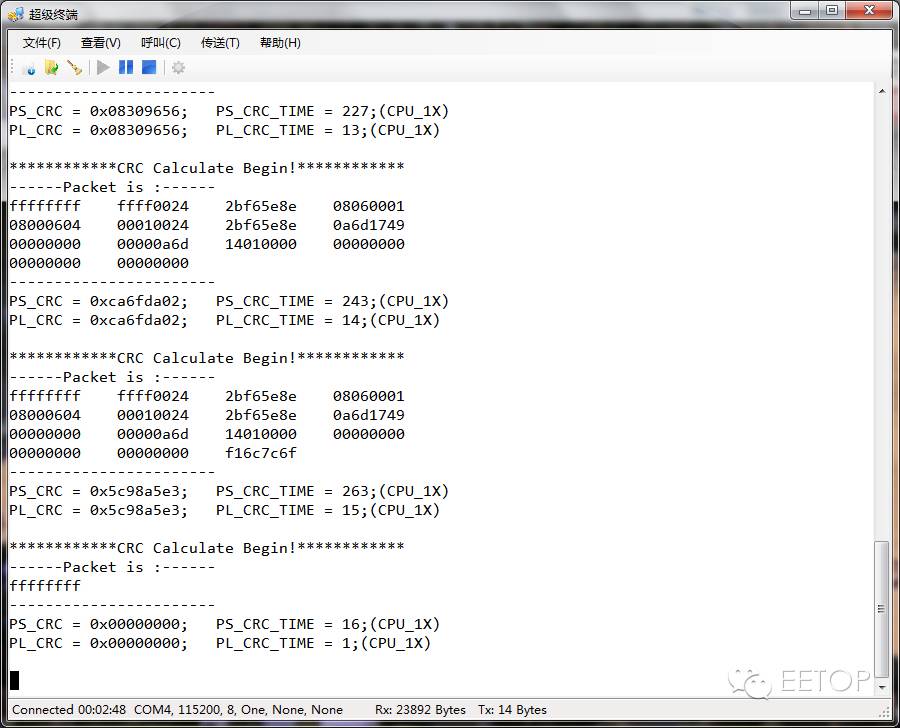

*CRC Calculate Begin!**************”

Ø随后输出本次PS与PL进行CRC校验的数据:

“---------Packet is :-----------”

“数据包内容”(32bit为一组)

“---------------------------------”

Ø首先输出PS端CRC校验结果以及计算时间:

“PS_CRC = 0x......; PS_CRC_TIME = ……”

Ø之后输出PL端CRC校验结果以及计算时间:

“PL_CRC = 0x......; PL_CRC_TIME = ……”

连续按下按键,则超级终端返回内容如下:

以上就是本题目的CRC算法比较流程以及PS端的实现方案,接下来介绍PL端的实现方法。

3.基于FPGA的CRC算法实现(PL端)

题目要求使用GP,HP,ACP总线完成数据帧的传输,如何完成数据帧的传输并界定帧的起始和截止是任务的重点。由于数据帧的长度并不大,也没有高速传输的要求,因此采用了最常用的GP总线。

实现方案:本人选择通过GP总线对自定义外设myip_crc_0中的4个控制/数据寄存器reg0~3进行读写,来完成数据帧的传输以及结果的返回功能。其中reg0为控制寄存器,包含标记帧起始的SOP和帧截止的EOP信号;reg1为数据寄存器,用于接收对端发送的32bit数据帧;reg2和reg3用于存储CRC校验的结果和消耗的时间。在一次帧传输开始后,所有接收的32bit数据会被自动存入FIFO中,当EOP信号有效时开始对FIFO内的全部数据进行连续的CRC校验并进行计时,校验完成后将结果存储到寄存器中并返回给PS端。

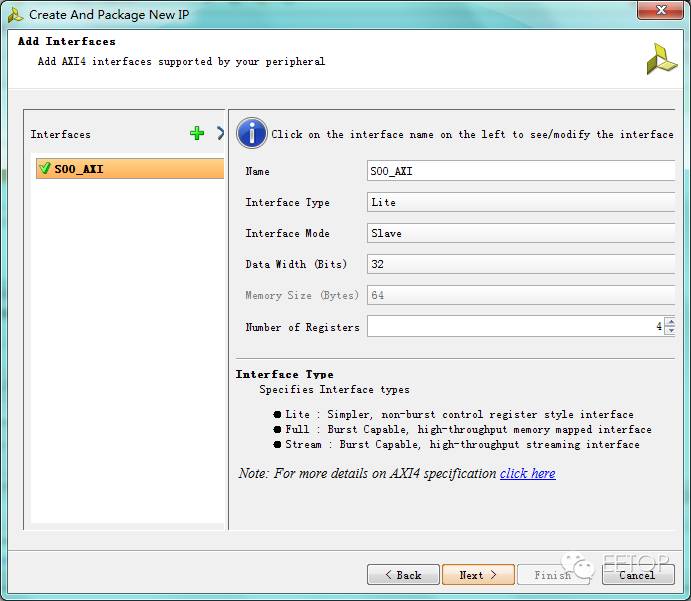

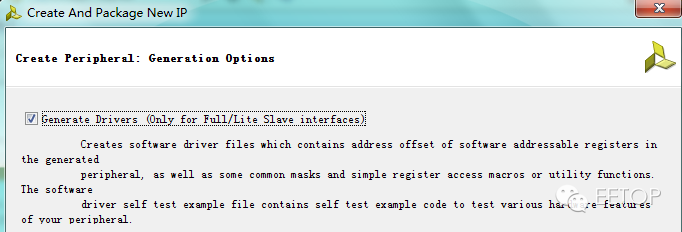

设计细节:生成带有AXI从接口的自定义IP核是本题目设计中的一个重点,需要选择好对应参数,并同时生成驱动以备软件使用:

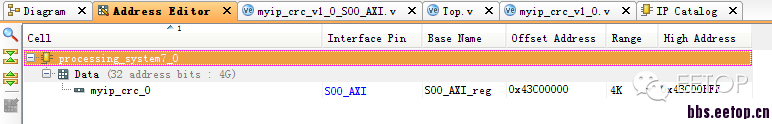

建立好新的IP后需要在AddressEditor中为其分配地址空间

然后进入IP Packager中对其进行各项配置

并且每次修改后记得进入“Reviewand Package”中点击”Re-package IP”进行保存。

IP核生成之后,下一步需要对AXI从接口模块源文件“myip_crc_v1_0_S00_AXI.v”进行部分修改并在其中例化自定义功能模块。该源文件包含AXI Slave接口中每个输入输出信号的含义注释以及AXI协议功能实现部分的代码注释,方便设计人员进行阅读和修改。

在myip_crc_v1_0_S00_AXI.v中除了例化自定义的模块外,对协议本身部分的代码也进行了少许修改,使寄存器reg0~reg3可以同时被PL端进行赋值,并且控制向reg1写入的数据自动写入FIFO中。当接收到EOP信号后,启动CRC运算,连续读取FIFO中的数据包并进行校验,直到FIFO读空后完成本次校验并将结果写入寄存器reg2、reg3中返回。

仿真结果:

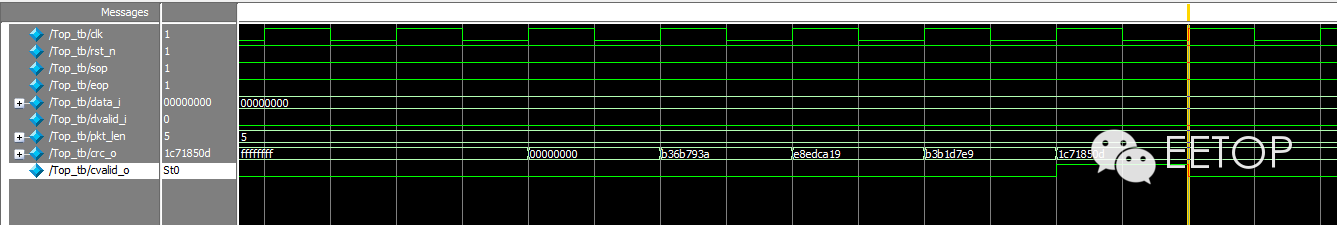

下图为数据包接收及校验过程仿真,测试的是数据包长度为五的情况

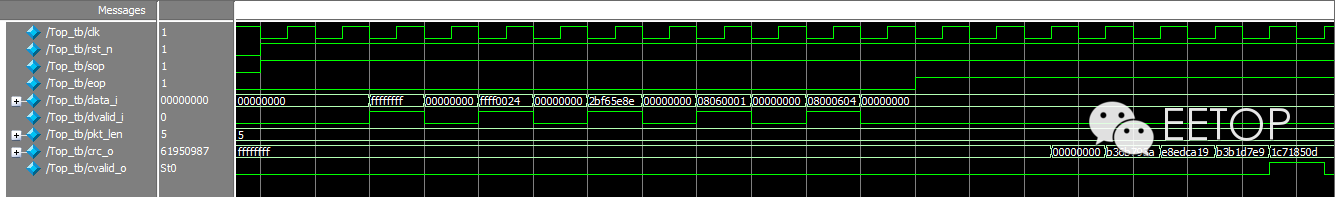

下图为五组连续的校验结果,与超级终端返回的初始五次比较结果吻合

以上便是PL端CRC算法的设计实现方法。

(三)总结

本次为期两周的Zynq极客挑战赛告于段落了,对于楼主来说这次比赛的挑战性还不小。困难主要体现在比赛之前我仅有过MicroBlaze + XPS的SOC经验,没有接触过Zynq器件和Vivado。在短时间内熟悉软硬件、设计流程需要十分专注的学习和尝试,并且寻找合适的学习资源。另外,时间也是一个问题,在挑战期间突发的事情会打乱设计调试的进度,真正用来进行开发的时间也就一个星期左右。优势在于之前是做计算机网络应用方面的,对题目二中CRC算法的FPGA设计实现有一定经验。最终,在规定的时间内完成了题目中的前四个要求,只是还有一些想法未能及时实现,比如使用MAC控制器从网络中实时抓取长度可变、内容较大的数据包进行CRC校验,使本次设计具有更大的应用意义并提高设计难度。

最后,再次感谢EETOP论坛给予本次挑战机会。希望越来越多的FPGA、嵌入式爱好者参与到其中,从中学习、思考、体验,收获更多的知识和技能。同时也祝愿中国的电子设计、制造行业能够迅速发展,不断进步!

ARMCRC算法FPG 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)