浅谈ARM架构1

ARM->Thumb:操作数寄存器状态为1,执行BX指令。

Thumb->ARM:操作数寄存器状态为0,执行BX指令。或者是处理器进行异常处理(IRQ,FIQ,Reset,Undef,Abort,SWI ARM状态执行)时,把pc指针放入异常模式链接寄存器中,并从异常向量地址开始执行程序,也可以使得处理器切换到ARM状态。

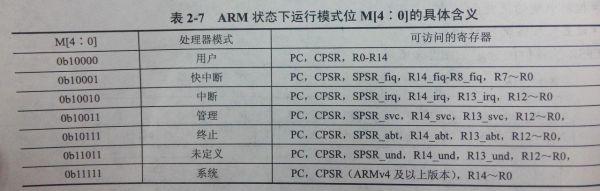

以上是整体指令集系统的情况,接下来说一下ARM处理器的运行模式。用过Linux的都知道,操作系统有很多运行模式,其实着很多的运行模式也是需要处理器支持的。ARM处理器的运行模式有七种:(除用户模式,别的均属于非用户模式或者特权模式;除了用户模式和系统模式,别的都称为异常模式)

用户模式(USR):正常状态;

快速中断模式(FIQ):用于高速数据传输或通道形式;

外部中断模式(IRQ):用于通用的中断处理;

管理模式(SVC):操作系统使用的保护模式;

数据访问终止模式(ABT):当数据或指令预取终止时进入该模式,可用于虚拟存储保护及存储保护;

系统模式(SYS):运行具有特权的操作系统任务;(Linux下就是root用户了)

未定义指令中断模式(UNDEF):当未定义的指令时进入该模式,可支持硬件协处理器的软件仿真。

那么我们为了实现以上的模式,我们在处理器这里资源应该如何分配呢?这里就涉及到寄存器组了。寄存器组就可以存储这些模式,并在该模式下操作所需要的数据。

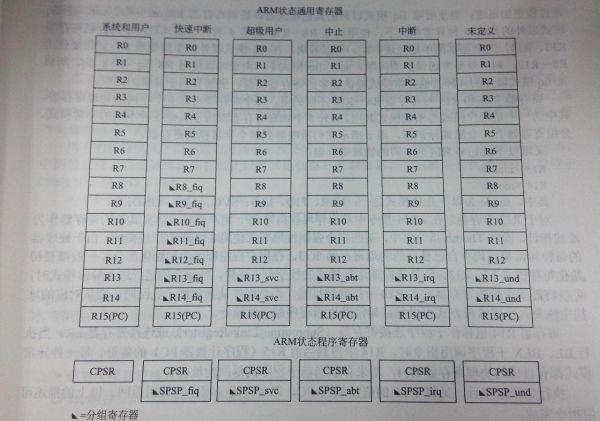

以下就是ARM指令集的寄存器组:

我们可以看到针对一些特定的模式寄存器组会有所改变。一共有37个32bit的寄存器。带三角形的就是分组寄存器,专用寄存器。快速中断的7个便于快速中断。R0~R7是未分组寄存器,通用。

当别的除了快速中断模式之外,别的模式因为要访问R8~R12,就有可能在模式转换的时候要保护现场。

一般来说,R13就是堆栈寄存器,当然指定别的寄存器也是可以的。

R14其实就是子程序链接地址,比如递归的时候,它里面存的就是返回地址。比如汇编的

MOV PC,LR

BX LR

以上就是实现了返回链接地址。另外R14还可以处理中断或者异常返回。

R15就是程序计数器(PC)。ARM的[31:2]来保存地址,因为是4个字节。Thumb指令集就是[31:1]是地址,[0]=0。因为只有两个字节,指令之间的地址就是相差2。由于是多级流水线设计,所以保存PC的时候要注意PC会因流水线而改变。

当然上面说了很多模式还有什么状态恢复,返回之前状态,堆栈处理啊其实和真正你在写处理器的时候不用管,因为很多功能是通过调度实现的,不用太在意更高抽象层次的东西。在这里说一下只是增加一些在处理器硬件低层实现之后如果完成那些复杂程序有更多的了解。

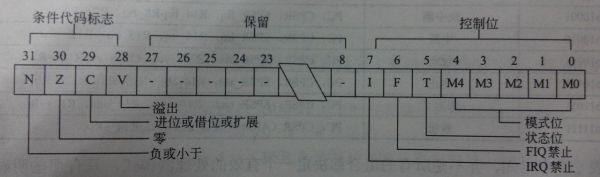

CPSR:也就是程序状态寄存器。这种寄存器就是存储整个程序执行的一个状态。包括了4 bit的条件代码标志(N,Z,C,V);2bit中断禁止位(分别用于一种类型的中断);5bit去对当前处理器操作模式进行编码的位;1bit用于指示当前执行的是Thumb还是ARM指令集。

如图:

中断禁止位:I,F

I = 1,禁止IRQ机制;F = 1,禁止FIQ机制。

T表示标志位,该位反应了处理器的运行状态。

如果模式不确定,那么就会导致进行复位。

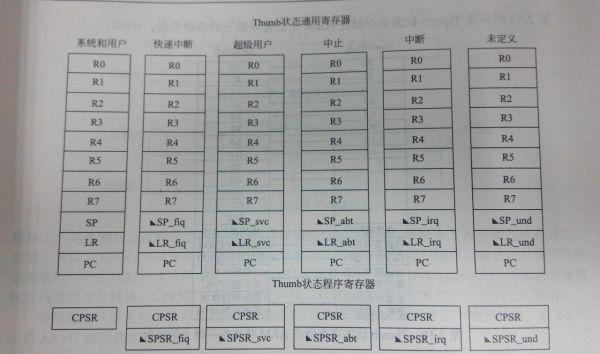

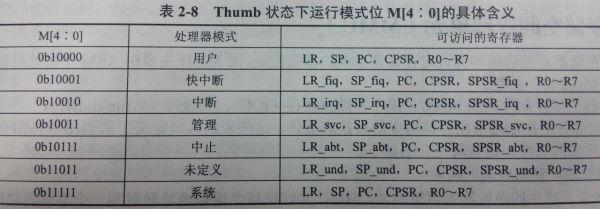

看一下Thumb指令集系统:

thumb指令集系统的模式位的含义:

ARM架 相关文章:

- ARM架构与体系学习(二)——3级流水线(11-21)

- ARM架构与体系学习(三)——ARM处理器状态(11-21)

- MIPS和ARM的架构比较(11-21)

- ARM架构MMU、存储管理器功能笔记(11-21)

- 基于arm架构单片机的hadoop服务器尝试(11-20)

- arm架构的linux内核中,clrex指令的作用是什么(11-10)