ARM处理器模式及寄存器

- 行ARM指令。

- T=1表示执行Thumb指令。

对于ARMv5以及更高的版本的非T系列的ARM处理器,T控制位含义如下:

- T=0表示执行ARM指令。

- T=1表示强制下一条执行的指令产生未定义指令中断。

3)M控制位

控制位M[4:0]控制处理器模式,具体含义如表3所示。

表3控制位M[4:0]的含义

M[4:0] | 处理器模式 | 可访问的寄存器 |

0b10000 | User | PC,R14一R0,CPSR |

0b10001 | FIQ | PC,R14_fiq-R8_flq,R7~R0,CPSR,SPSR_nq |

0b10010 | 1RQ | PC,R14 _irq-R13 _irq,R12一R0,CPSR,SPSR_ irq |

0b10011 | Supervisor | PC,R14_ svc-R13 _svc,R12~R0,CPSR,SPSR_svc |

0b10111 | Abort | PC,R14_abt-R13_abt,R12~R0,CPSR,SPSR_abt |

0b11011 | Undefined | PC,R14_und-R13_und,R12~R0,CPSR,SPSR_ und |

4.CPSR中的其他位

CPSR中的其他位用于将来ARM版本的扩展。应用软件不要操作这些位,以免与ARM将来版本的扩展冲突。

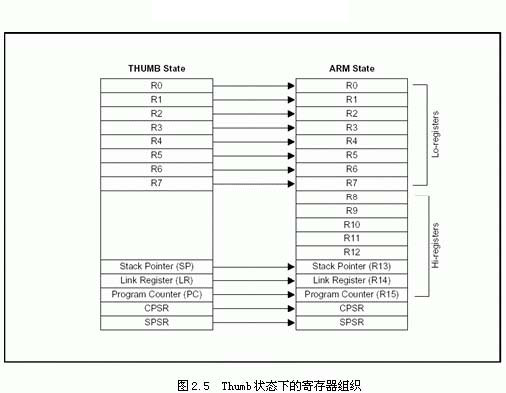

(二)Thumb工作状态下的寄存器组织

Thumb状态下的寄存器集是ARM状态下寄存器集的一个子集,程序可以直接访问8个通用寄存器(R7~R0)、程序计数器(PC)、堆栈指针(SP)、 连接寄存器(LR)和CPSR。同时,在每一种特权模式下都有一组SP、LR和SPSR。图2.4表明Thumb状态下的寄存器组织。

Thumb状态下的寄存器组织与ARM状态下的寄存器组织的关系:

─ Thumb状态下和ARM状态下的R0~R7是相同的。

─ Thumb状态下和ARM状态下的CPSR和所有的SPSR是相同的。

─ Thumb状态下的SP对应于ARM状态下的R13。

─ Thumb状态下的LR对应于ARM状态下的R14。

─ Thumb状态下的程序计数器对应于ARM状态下R15

以上的对应关系如图2.5所示:

访问THUMB状态下的高位寄存器(Hi-registers):

在Thumb状态下,高位寄存器R8~R15并不是标准寄存器集的一部分,但可使用汇编语言程序受限制的访问这些寄存器,将其用作快速的暂存器。使用带特殊变量的MOV指令,数据可以在低位寄存器和高位寄存器之间进行传送;高位寄存器的值可以使用CMP和ADD指令进行比较或加上低位寄存器中的值。

ARM处理器模式寄存 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)