CC1101接口与STM32

移植原来TI对于CC1101与MSP430接口库到STM32平台,参考原TI库应用笔记“ MSP430 Interface to

CC1100/2500 Code Library”,做到尽量保持所有函数名不改变,以方便以前基于MSP430的程序向STM32移植。

1.编程要求:改写原来基于MSP430的程序,使用于STM32,尽量保持所有函数名不改变,以方便以前基于MSP430的程序向STM32移植。

2.实现功能:STM32与CC1101通过SPI接口正常传输数据,不同节点的CC1101可以正常传输数据。

3.实验现象:STM32与CC1101连接后,可以与另一个节点通信,节点初始在随机时间发送一个数据,任一节点收到数据后LED闪一下,并把数据回传,如此循环,会看到LED不停闪烁。

CC1101是TI公司一款高性价比的单片UHF收发器,为低功耗无线电应用而设计。它是CC1100器件的加强升级版,灵敏度更高,功耗更小,带宽更大。CC1101可满足多个领域中的低功耗无线应用要求,如警报与安全、自动抄表、工业监控以及家庭和楼宇自动化等。CC1101理想适用于工业、科学及医药设备(ISM)以及316、433、868及916MHz短距装置(SRD)频带。但是,该器件也可方便编程,以支持其它频率,如300-348MHz、387-467MHz及779-928MHz等。出色的频带与调制格式支持使其能与目前的RF终端设备相兼容。

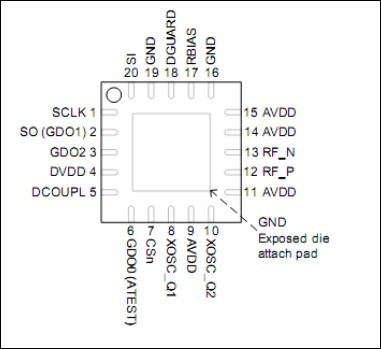

图1 CC1101 的外引脚图(俯视)

CC1100通过4线SPI兼容接口 (SI,SO,SCLK和 CSn)配置。这个接口同时用作写和读缓存数据。SPI

接口上所有的处理都同一个包含一个读/写位,一个突发访问位和一个 6 位地址的头字节一起作用。在地址和数据转换期间, CSn 脚

(芯片选择,低电平有效)必须保持为低电平。如果在过程中 CSn 变为高电平,则转换取消。当 CSn 变低, 在开始转换头字节之前,

MCU必须等待,直到 SO脚变低。这表明电压调制器已经稳定,晶体正在运作中。除非芯片处在 SLEEP 或 XOFF 状态,SO 脚在

CSn变低之后总会立即变低。关于CC1101对配置寄存器写和读操作如图2所示。

芯片状态位

当头字节在 SPI 接口上被写入时,芯片状态字节在 SO 脚上被 CC1100 写入。状态字节包含关键状态信号,对MCU是有用的。第一位

s7,是CHIP_RDYn 信号。在 SCLK的在第一个正边缘之前,这个信号必须变低。CHIP_RDYn

信号表明晶体正处于工作中,调节数字供给电压是稳定的。6,5 和4 位由状态值组成。这个值反映了芯片的状态。 当使 XOSC

空闲并使数字中心的能量开启,所有其他模块处于低功耗状态时。只有芯片处于此状态时,频率和信道配置才能被更新。当芯片处于接收模式时,

RX状态是活动的。同样地,当芯片处于发送模式时,TX状态是活动的。状态字节中的后四位( 3

:0)包含FIFO_BYTES_AVAILABLE。为了进行读操作,这个区域包含可从 RX FIFO

读取的字节数。为了进行写操作,这个区域包含可写入 TX FIFO 的 字节数。

寄存器访问

CC1100配置寄存器位于SPI地址从0x00到0x2F之间。所有的配置寄存器均能读和写。当对寄存器写时,每当一个待写入的数据字节传输到

SI脚时,状态字节将被送至 SO脚。

通过在地址头设置突发位,连续地址的寄存器能高效地被访问。这个地址在内部计数器内设置起始地址。每增加一个新的字节计数器值增加 1。

突发访问,不管是读访问还是写访问,必须通过设置CSn 为高来终止。对 0x30-0x3D间的地址来说,

突发位用以在状态寄存器和命令滤波之间选择。状态寄存器只读。突发读取对状态寄存器是不可取的,故它们每次只能被读一个。

命令滤波

命令滤波可被视为 CC1100

的单字节指令。通过命令滤波寄存器的选址,内部序列被启动。这些命令用来关闭晶体振荡器,开启传输模式和电磁波激活等。命令滤波寄存器的访问和一个寄存器的写操作一样,但没有数据被传输。就是说,只

有 R/W 位(置为 0) ,突发访问(置为 0)和六个地址位(0x30和0x3D之间)被写。一个命令滤波可能在任何其他 SPI

访问之后,而不需要将 CSn 拉至高电平。命令滤波立即被执行,当 CSn 高时 SPWD和 SXOFF滤波是例外。

FIFO访问

64 字节 TX FIFO 和 64 字节 RX FIFO 通过0x3F 被访问。当读/写位为 0 时,TX FIFO被访问,当读/写位为 1

时,RX FIFO 被访问。 TX FIFO是只写的,而 RX FIFO是只读的。突发位用来决定 FIFO

访问是单字节还是突发访问。单字节访问方式期望地址的突发位为 0 及1

数据字节。在数据字节之后等待一个新的地址,因此,CSn继续保持低。突发访问方式允许一地址字节,然后是连续的数据字节,直到通过设置 CSn

为高来关断访问。 当对 TX FIFO写时,状态字节对每个 SO脚上的新数据字节是输出量,如图 6 所示。这个状态位能用来侦测对 TX FIFO

写数据时的下溢。注意,状态字节包含在写入字节到 TX FIFO 的过程前空闲的字节数。当最后一个适合 TX FIFO的字节被传送至 SI 脚后, 被

SO脚接收的状态位会表明在 TX FIFO中只有一个字节是空闲的。

传输 FIFO 可能会通过发布一个 SFTX 命令滤波而被淹没。相似地,一个 SFRX命令滤波会淹没接收 FIFO。当进入休眠状态时, 两个

FIFO都被清空。PATABLE 访问

0x3E 地址用来访问 PATABLE。PATABLE用来选择 PA 能量控制设置。在接收此地址之后,SPI 等待至少 8

个字节。通过控制PATABLE,能实现可控的 PA能量上升和下降,减少的带宽的 ASK 调制整型也如此PATABLE 是一个 8 字节表, 定义了

PA控制 设置, 为 8 个 PA 功率值(由FRENDO.PA_POWER 的 3

个位的值所选择)的每一个所使用。这个表从最低位到最高位可读和写,一此一位。一个索引计数器用来控制对这个表的访问。每读出或写入表中的一个字节,计数器就加

1。当 CSn 为高时,计数值置为最小值。当达到最大值时,计数器由零重新开始计数。

PATABLE 访问

对 PATABLE

的访问是单字节或者突发访问,由突发位决定。当使用突发访问时,索引计数器的值增加;达到7时重新从0开始。读/写位控制访问是写访问(R/W=0)或者读访问(R/W=1)。

如果一字节被写入 PATABLE,且这个值将要被读出,那么,为了设置索引计数器的值重为 0,CSn必须在读访问之前置为高。 注意,当 PATABLE

进入休眠状态时,所存储的内容会丢失,特别是第一个字节。

图2 配置寄存器写和读操作

STM32的串行外设接口(SPI)

STM32的串行外设接口(SPI)有如下特性:

● 3线全双工同步传输

● 带或不带第三根双向数据线的双线单工同步传输

● 8或16位传输帧格式选择

● 主或从操作

● 支持多主模式

● 8个主模式波特率预分频系数(最大为fPCLK/2)

● 从模式频率 (最大为fPCLK/2)

● 主模式和从模式的快速通信

● 主模式和从模式下均可以由软件或硬件进行NSS管理:主/从操作模式的动态改变

●

CC1101接口STM3 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)