s3c2440 存储系统和I/O空间 认识

时间:11-11

来源:互联网

点击:

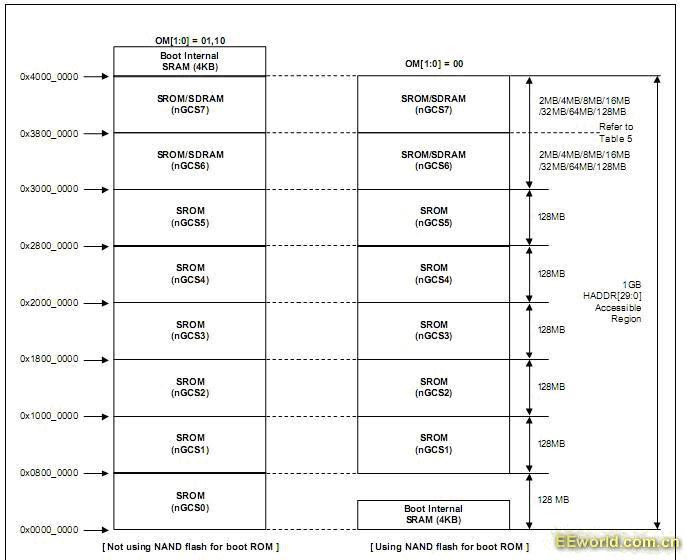

用3根地址线译码出来的.所以一共用了30根地址线,30根不正好是1G么.呵呵.

说的差不多了.应该有很多需要完善的,但是这对于初学者来说还是有一定的帮助吧?

S3C2440 MEMORY CONTROLLER详解

BANK0总线宽度由OM[1:0]引脚决定,当OM[1:0]=01时,booting ROM data width是16位,当[1:0]=10时,booting ROM data width是32位,当OM[1:0]=00时,从NAND FLASH启动。在友善之臂S3C2440开发板上,OM1引脚直接接地。

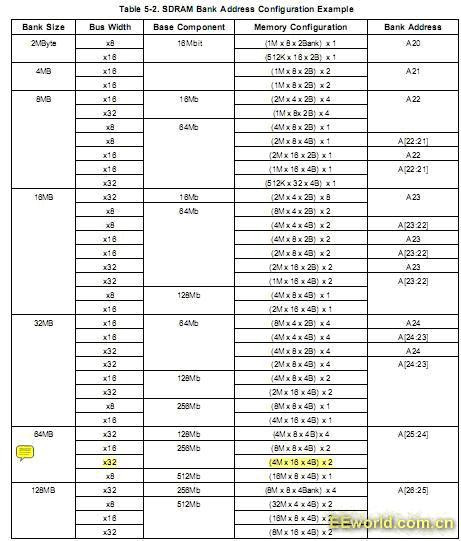

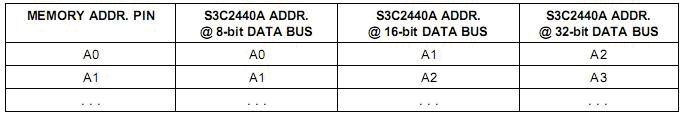

依据这张表,可以查找到SDRAM的BANK选择引脚连接方式,比如,我们使用的SDRAM是2片HYNIX的HY57V561620(L)T,它的规格是4*4M*16bit(使用两片是为了配置成32位的总线宽度),BANK大小是4M*16=64MB,总线宽度是32位,器件大小是4*BANK大小=256Mb(M bit的意思吧),寄存器配置就是(4M*16*4B)*2( M bit ),根据上面的表格,SDRAM上的BANK地址引脚(BA[1:0])与S3C2440的A[25:24]相连。

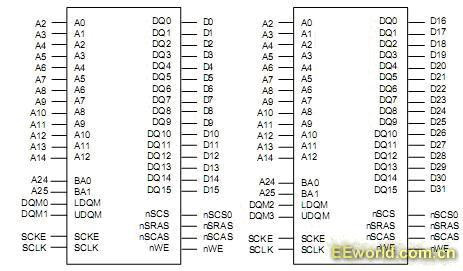

具体的S3C2440与两片SDRAM接线方式如下图所示:

SDRAM的工作时序作为ARM工程师了解即可,具体的读写控制由寄存器控制器完成,作为FPGA工程师则需要详细了解SDRAM工作原理与时序,在此不再赘述。作为ARM工程师,最重要的是准确配置与SDRAM相关的寄存器。

软件可编程的大小端模式;

地址空间:每个BANK可寻址128MB(总共8个BANK 1GB空间);

可编程的访问位宽:BANK0为16或32位,其他BANK为8或16或32位;

8个存储器BANK,其中6个用于ROM或者SRAM,2个用于ROM、SRAM或者SDRAM;

BANK0~BANK6的起始地址固定;

BANK7的起始地址和大小可编程;

所有存储器BANK的访问周期可编程;

外部wait信号可延长总线周期;

支持SDRAM的自刷新和掉电模式。

s3c2440存储系统IO空 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)