STM8 中断控制器ITC

中断控制器提供如下功能:

● 硬件中断的管理

─ 所有I/O 引脚都具有外部中断能力,每一个端口都有独立的中断向量以及独立的标志。

─ 外设中断能力

● 软件中断的管理(TRAP)

● 具有灵活的优先级和中断等级管理,支持可嵌套的或同级中断管理:

– 多达4个软件可编程的嵌套等级

– 最多有32个中断向量,其入口地址由硬件固定

– 2 不可屏蔽的事件: RESET, TRAP

– 1 个不可屏蔽的最高优先级的硬件中断 (TLI)

基于如下资源的中断管理:

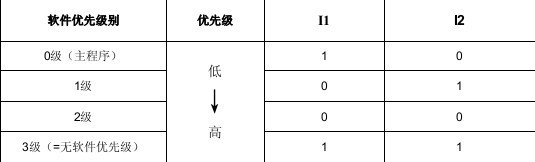

● 位I1 和I0 位于CPU的条件代码寄存器(CCR)

● 软件优先级寄存器 (ITC_SPRx)

● 复位向量地址0x00 8000 位于程序空间的起始部分。对于具有启动ROM的型号,ST公司把复位初始化程序固化在ROM区中。

● 固定的中断向量地址位于程序空间映像的高位地址段(0x00 8004 to 0x00 807C) ,其地址顺序即为硬件的优先顺序。

中断屏蔽和处理流程

中断屏蔽是通过CC寄存器的位I1 和位I0 以及设置每个中断向量( 表13) 的软件优先级的ITC_SPRx来管理的。处理流程如图所示:

当一个中断请求必须被响应时:

1. 在当前正在执行指令结束之后,正常的操作被悬起;

2. PC,X,Y,A和CC寄存器被自动压栈;

3. 根据ITC_SPRx 寄存器中的值对应的中断服务向量,CC寄存器中的位I1 和I0 被相应设置;

4. 通过中断向量载入中断服务子程序的入口地址,接着对中断服务子程序的第一条指令取址( 参考表中断映射表 来了解向量地址的更详细情况)。

中断服务子程序必须以IRET指令结束,该指令会把堆栈中的保存的寄存器内容出栈,同时由于运行IRET 指令,位I1 和位I0 被重新恢复,程序也恢复运行。

处理等待(排队)的中断

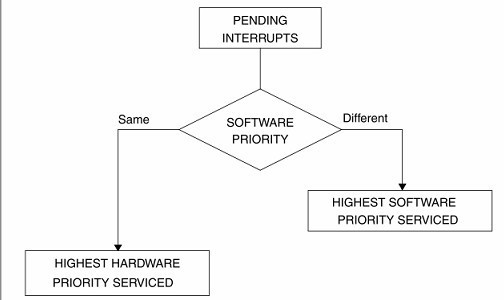

同一时间可以有几个中断排队等待处理。中断响应是根据如下两步来决定的:

1、最高软件优先级的中断被响应;

2、如果几个排队的中断具有相同的软件优先级,那么最高硬件优先级的中断先响应。

当中断请求没有立即得到响应时,该中断请求被锁存;当其软件优先级及硬件优先级均为最高的时候,该中断被处理。

注意:

1、与软件优先级不同,每个中断的硬件优先级是唯一且互不相同的,这样就可保证一个时刻只有一个中断被唯一确定地处理。

2、RESET, TLI 和 TRAP 这个几个中断被认为是拥有最高的软件优先级来处理。

3、一个TLI中断可中断除TRAP 及RESET之外的3级中断。

见图了解更加详细的排队等待处理的中断服务过程。

中断源

STM8 中断控制器处理2种类型的中断源:

● 不可屏蔽的中断: RESET ,TLI 和 TRAP

● 可屏蔽中断: 外部中断或者内嵌的外设中断

不可屏蔽中断源

不可屏蔽中断不会考虑CC寄存器的I1 和I0 的状态(参见图) 。仅仅当TRAP 中断发生时候将PC, X, Y, A 和 CC 寄存器的内容压栈。相应的向量载入到PC寄存器中同时置位I1 和I0 位禁止中断(3级优先级)。

● TRAP (不可屏蔽的软件中断)

当执行TRAP 指令时就响应软件中断。它响应过程如图所示的流程图。

TRAP 中断不能使处理器从停机(Halt) 模式下退出。

● RESET 复位

复位中断是STM8 的软件和硬件中断的最高优先级,这也就是说在复位程序的开始所有的中断被禁止。必须通过RIM 指令来使能它们(见表)。

复位中断可以使处理器从停机(Halt) 模式退出。

更详细的复位中断管理见复位章节。

● TLI最高等级的硬件中断

当在特定的 I/O 边沿检测到在相应的TLI输入时将产生硬件中断。

注意: 在TLI中断服务子程序中禁止使用TRAP 指令。

可屏蔽的中断源

对于可屏蔽中断,如果相应的中断被使能,而且如果在ITC_SPRx 寄存器的中断优先级比当前正在执行的中断(根据CC寄存器的I1 和I0 位)的优先级高的话那么就可以被响应。如果上面2个条件中 的任何一个不满足那么该中断会被锁存并保持在等待状态。

● 外部中断

外部中断可以用来把MCU从停机(Halt) 模式唤醒。外部中断触发方式的选择可以通过软件写控制外部中断控制寄存器(EXTI_CRx) 来实现。

当多个连接到同一个中断向量的外部引脚中断被同时选定时候,那么他们是‘逻辑或’的关系。

当外部的电平触发中断被锁存后,如果该给定的电平一直保持到中断子程序结束,那么该电平信号将再次触发中断,除非在中断子程序中禁用该中断。

● 外设中断

大部分的外设中断会导致MCU从停机(Halt) 模式下唤醒。见表。

当对应外设状态寄存器的中断标志位被置位,同时相应的外设控制寄存器的使能位被置位时将产生一个外设中断。

清除一个外设中断的标准顺序是在对状态寄存器的访问后再对相关寄存器进行读或者写操作。

当一个清除过程被执行之后相应的悬起中断(一个将被执行的中断)会丢失。

中断和低功耗

STM8中断控制器IT 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)