S3C2440的LCD简单应用与实现

TFT LCD的TTL信号

VSYNC 垂直同步信号

HSYNC水平同步信号

HCLK 像素时钟信号

VD[23:0] 数据信号

LEND 行结束信号(非必须)

PWREN 电源开关信号

显示器上的数据组成格式

一幅图像被称为一帧(frame),每帧由多行组成,每行有多个像素组成,每一个像素的颜色用若干位的数据来表示。对于单色显示器,每个像素使用1位来表示,称为1BPP;对于256色显示器,每个像素使用8位来表示,称为8BPP.

显示器从屏幕左上方开始,一行一行地取得每个像素的数据并显示出来,当显示到一行的最右边时,跳到下一行的最左边开始显示下一行,当显示完所有行时,跳到左上边开始下一帧。显示器沿着“Z”字行的路线进行扫描,使用HSYNC、VSYNC信号来控制扫描路线跳转,HSYNC表示“是跳到最左边的时候了”,VSYNC表示“是跳到最上边的时候了”。

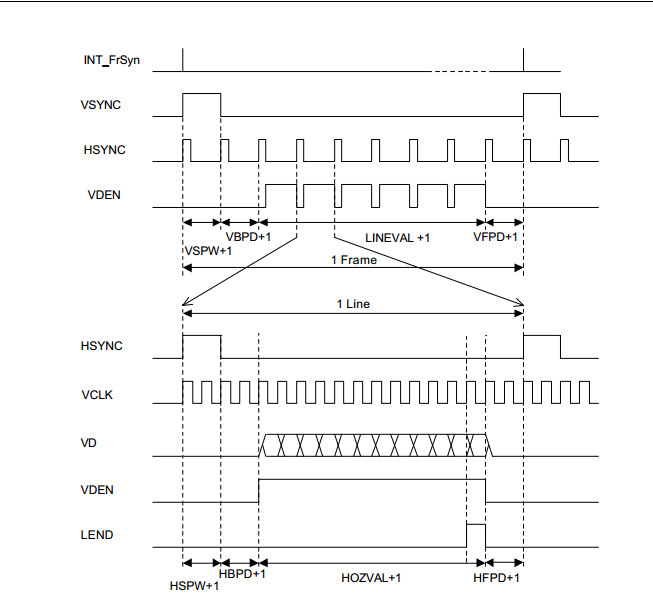

VSYNC信号出现的频率表示一秒钟内能显示多少帧图像,称为垂直频率或者场频率。就是常说的“显示器频率”;HSYNC信号出现的频率称为水平频率。现在来看一下时序图。

VSYNC可以理解为一帧图像有效地信号,在它低电平有效的时候,要连续发出(LINEVAL+1)个行有效数据HSYNC信号;而在HSYNC有效地时候,要连续发出(HOZVAL+1)个像素有效数据,这时像素数据的频率是由VCLK控制,VCLK是作为时序图的基准信号。我们开发板上用的屏是240*320的3.5寸触摸屏,那么LINEVAL+1=240,HOZVAL+1=320。开始时,对垂直频率理解很模糊,后面干脆理解为一帧图像有效地信号,这样正好与它的“显示器频率”相对应。在时序图中,可以看见VSWP/VBPD/VFPD和HSPW/HBPD/HFPD这几个参数,这是由于LCD在工作中往往四周会有黑框,我们通过设置这几个参数,可以控制使LCD的实际显示区域(数据有效区)与屏幕大小相当,这样就看不到黑框。

VSPW表示VSYNC信号的脉冲宽度为(VSPW+1)个HSYNC信号周期,即VSPW+1行,这VSPW+1行数据无效。

VSPD表示VSYNC信号脉冲之后,还要经过VSPD+1个HSYNC信号周期,有效行才出现。

VFPD表示在连续发出LINEVAL+1行有效数据后,还要经过VFPD+1个无效行,之后完整的一帧结束。

HSPW表示HSYNC信号脉冲宽度为(HSPW+1)个VCLK信号周期,即HSPW+1个像素是无效的。

HBPD表示在HSYNC信号脉冲之后,还要经过HBPD+1个VCLK信号周期,有效像素才能够出现。

HFPD表示在连续发出HOZVAL+1个像素的有效数据之后,还要发出(HFPD+1)个无效像素,完整的一行结束。

VCLK是像素时钟,计算公式如下:

VCLK=HCLK/[(CLKVAL+1)*2]

CLKVAL可以通过LCDCON1设置,HCLK是100MHz,根据驱动的LCD的像素时钟为6.4MHz,代入得到CLKVAL值为6.8,取整后(6)存入到LCDCON1中,此时得到的VCLK为7.1MHz。

现在看一下场频(VSF)和行频(HSF)的计算公式:

HSF=VCLK/[(HSPW+1)+(HSPD+1)+(HFPD+1)+(HOZVAL+1)]=7.1/408=17.5KHz

VSF=HSF/[(VSPW+1)+(VBPD+1)+(VFPD+1)+(LINEVAL+1)]=17.5/270=64.8Hz

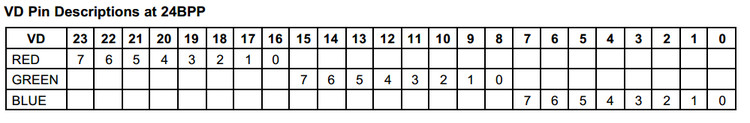

接下来了解一下24BPP模式下图像数据格式。

现在设置好VSYNC、HSYNC、VCLK等信号的参数之后,并将帧内存(frame memory)d地址告诉LCD控制器,它即可自动的发起DMA传输从帧内存中得到图像数据,最终在上述信号的控制下出现在数据总线VD[23:0]上。在内存中使用4个字节(32位)来表示一个像素,其中的3个字节从高到低分别表示红、绿、蓝,剩余的一个字节无效。是低字节还是高字节无效,可以通过LCDCON5[12]来设置,设置为0,低字节有效,设置为1,高字节有效。

----------------------------------------------------------华丽分割------------------------------------------------------------------------------------------

现在还要说一个问题就是显示缓存区。这是要用到三个帧内存地址寄存器LCDSADDR1~LCDSADDR3

先来看一下帧内存与视口(view point)对应关系。视口就是要真正显示的区域

关于缓存区(内存地址)我们定义一个二维数组LCD_BUFFER[240][320],来存储像素数据。在LCDSADDR1中,用来保存帧内存的起始地址,视口所对应的内存起始地址。看一下具体寄存器格式:

可以看出,帧内存地址A[30:22]对应LCDBANK[29:21],视口的起始地址

S3C2440LC 相关文章:

- 六 ARM9(S3C2440)的LCD显示-理论知识(11-27)

- S3C2440的LCD编程(11-27)

- s3c2440的LCD应用(11-24)

- S3C2440 LCD字符显示(11-21)

- ARM9(S3C2440)的LCD显示——理论知识(11-21)

- 嵌入式Linux之我行——S3C2440上LCD驱动(FrameBuffer)实例开发讲解(11-20)