LPC1114外部中断

LPC1114的每一个引脚都可以响应一个外部中断,所以有多少个引脚就有多少个外部中断。但LPC1114的中断系统非常强大,外部中断只是它其中的一小部分。因此,要用好外部中断,就必须先来了解LPC1114的整个中断系统。下面就来看一下它的中断系统。

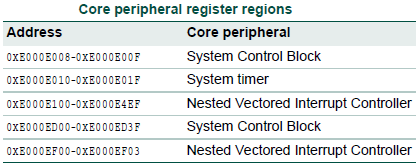

在LPC11xx系列处理器中,有一个部分被称为“私有外设总线”(Private peripheral bus),它位于Memory map中地址为0xE0000000~0xE0100000的地方,包含有下表中的几个核心外设。

其中的Nested Vectored Interrupt Contorller(NVIC)就是中断系统,被称为“内嵌套向量中断控制器”。它与处理器内核紧密耦合,可实现低中断延迟及对新中断的有效处理。它具有以下特征:

拥有32路向量中断;每个中断的优先级均可编程设置为0~192(步长64),数值越小优先级越高,0级为最高优先级;支持电平和边沿触发中断;支持中断尾链;拥有一个外部不可屏蔽中断NMI。

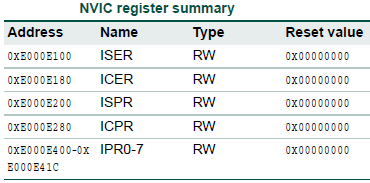

NVIC所涉及到的寄存器如下表所示。

从表中可以看出,每个寄存器都是32位的结构,都具有可读可写的属性,复位值都为全0。其中ISER寄存器是设置中断的使能,32位对应32路中断,值为1使能中断,值为0不使能中断。ICER寄存器是设置中断的禁能,32位对应32路中断,值为1禁能中断,值为0不禁能。ISPR寄存器是设置中断的挂起,32位对应32路中断,值为1挂起,值为0不挂起。ICPR寄存器是清除中断的挂起,32位对应32路中断,值为1清除挂起,值为0不清除挂起。IPR0~7寄存器是设置中断优先级。

下面是NVIC寄存器组所对应的结构体形式(位于头文件core_cm0.h中)。

typedef struct

{

__IO uint32_t ISER[1]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */

uint32_t RESERVED0[31];

__IO uint32_t ICER[1]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */

uint32_t RSERVED1[31];

__IO uint32_t ISPR[1]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */

uint32_t RESERVED2[31];

__IO uint32_t ICPR[1]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */

uint32_t RESERVED3[31];

uint32_t RESERVED4[64];

__IO uint32_t IP[8]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register */

} NVIC_Type;

因NVIC寄存器组的基址为0xE000E100,所以要将基址指针强制转换为上述结构体,还必须要加上下面的定义。

#define SCS_BASE (0xE000E000UL) /*!< System Control Space Base Address */

#define NVIC_BASE (SCS_BASE + 0x0100UL) /*!< NVIC Base Address */

#define NVIC ((NVIC_Type *) NVIC_BASE ) /*!< NVIC configuration struct */

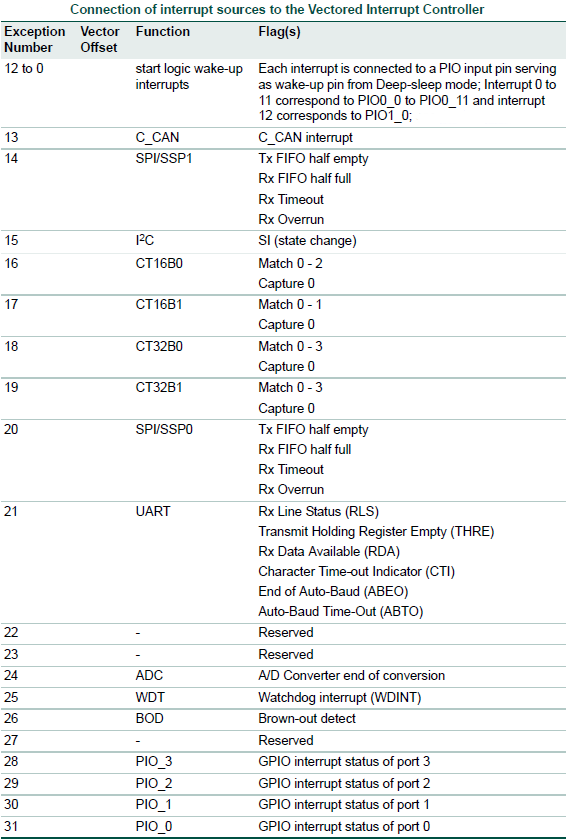

接下来给出的是上面NVIC32位寄存器所对应的32路中断向量的中断源。

为了能描述上面的32路中断源,在C语言中运用了枚举类型,代码如下所示(位于头文件lpc11xx.h中)。

typedef enum IRQn

{

/****** Cortex-M0 Processor Exceptions Numbers ***************************************************/

NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

HardFault_IRQn = -13, /*!< 3 Cortex-M0 Hard Fault Interrupt */

SVCall_IRQn = -5, /*!< 11 Cortex-M0 SV Call Interrupt */

PendSV_IRQn = -2, /*!< 14 Cortex-M0 Pend SV Interrupt */

SysTick_IRQn = -1, /*!< 15 Cortex-M0 System Tick Interrupt */

/****** LPC11xx/LPC11Cxx Specific Interrupt Numbers **********************************************/

WAKEUP0_IRQn = 0, /*!< All I/O pins can be used as wakeup source. */

WAKEUP1_IRQn = 1, /*!< There are 13 pins in total for LPC11xx */

WAKEUP2_IRQn = 2,

WAKEUP3_IRQn = 3,

WAKEUP4_IRQn = 4,

WAKEUP5_IRQn = 5,

WAKEUP6_IRQn = 6,

WAKEUP7_IRQn = 7,

WAKEUP8_IRQn = 8,

WAKEUP9_IRQn = 9,

WAKEUP10_IRQn = 10,

WAKEUP11_IRQn = 11,

WAKEUP12_IRQn = 12,

CAN_IRQn = 13, /*!< CAN Interrupt */

SSP1_IRQn = 14, /*!< SSP1 Interrupt */

I2C_IRQn = 15, /*!< I2C Interrupt */

TIMER_16_0_IRQn = 16, /*!< 16-bit Timer0 Interrupt */

TIMER_16_1_IRQn = 17, /*!< 16-bit Timer1 Interrupt */

TIMER_32_0_IRQn = 18, /*!< 32-bit Timer0 Interrupt */

TIMER_32_1_IRQn = 19, /*!< 32-bit Timer1 Interrupt */

SSP0_IRQn = 20, /*!< SSP0 Interrupt */

UART_IRQn = 21, /*!< UART Interrupt */

Reserved0_IRQn = 22, /*!< Reserved Interrupt */

Reserved1_IRQn = 23,

ADC_IRQn = 24, /*!< A/D Converter Interrupt */

WDT_IRQn = 25, /*!< Watchdog timer Interrupt */

BOD_IRQn = 26, /*!< Brown Out Detect(BOD) Interrupt */

FMC_IRQn = 27, /*!< Flash Memory Controller Interrupt */

EINT3_IRQn = 28, /*!< External Interrupt 3 Interrupt */

EINT2_IRQn = 29, /*!< External Interrupt 2 Interrupt */

EINT1_IRQn = 30, /*!< External Interrupt 1 Interrupt */

EINT0_IRQn = 31, /*!< External Interrupt 0 Interrupt */

} IRQn_Type;

LPC1114外部中 相关文章:

- LPC1114_外部中断程序_MDK编译环境(11-29)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)