S3C2440中断体系结构

1)ARM体系CPU的7种工作模式

用户模式(usr):ARM处理器正常的程序执行状态

快速中断模式(fiq):用于高速数据传输或通道处理

中断模式(irq):用于通用的中断处理

管理模式(svc):操作系统使用的保护模式

数据访问终止模式(abt):当数据或指令预取终止时进入该模式,可用于虚拟存储及存储保护

系统模式(sys):运行具有特权的操作系统任务

未定义指令中止模式(und):当未定义的指令执行时进入该模式,可用于支持硬件协处理器的软件仿真

除用户模式外,其他6种工作模式都属于特权模式,大多数程序运行于用户模式,进入特权模式是为了处理中断、异常,或者访问被保护的系统资源。

ARM体系的CPU有以下两个工作状态

ARM状态:此时处理器执行32位的字对齐的ARM指令

Thumb状态:此时处理器执行16位的、半字对齐的Thumb指令

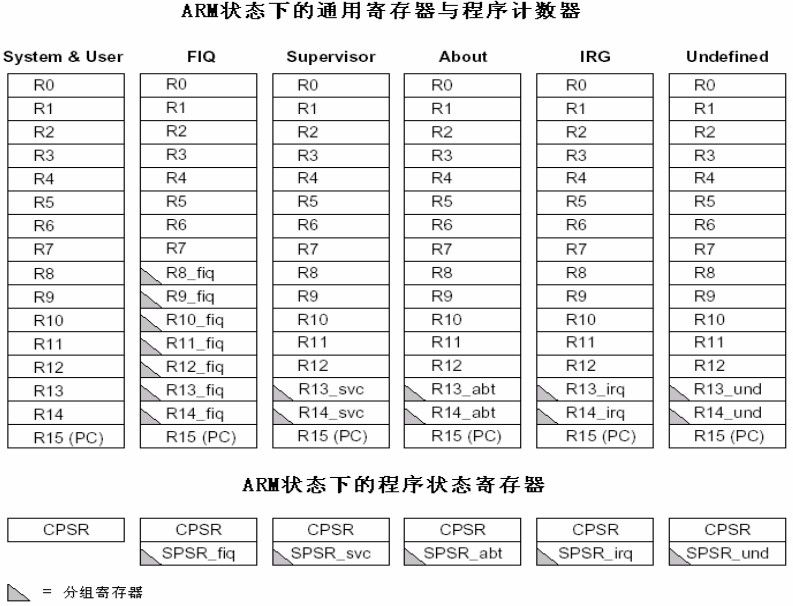

ARM920T有31个通用的32位寄存器和6个程序状态寄存器。这37个寄存器分为7组,如下图所示:

图中R0-R15可以直接访问,这些寄存器除了R15外都是通用寄存器,既可以保存地址也可以保存数据。

R13称为栈指针寄存器,通常用于保存栈指针

R14称为程序连接寄存器(LR),当执行BL子程序调用指令时,R14得到R15(程序计数器PC)的备份。

而当发生中断或异常时,对应的R14_svc,R14_irq,R14_abt或R14_und中保存R15的返回值

R15是程序计数器

快 速中断模式有7个备份寄存器R8_fiq-R14_fiq,这使得进入快速中断模式执行很大部分程序时(不改变R0-R7),不需要保存任何寄存器。用户 模式、管理模式、数据访问终止模式和未定义指令中止模式都含有两个独占的寄存器副本R13、R14,这样令每个模式拥有自己的栈指针寄存器和连接寄存器。

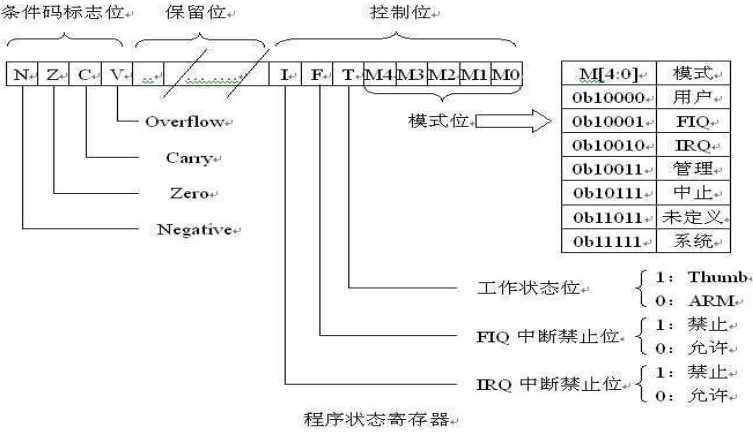

每种工作模式还有寄存器CPSR(当前程序状态寄存器),它被用于标识各种状态和当前处于哪种工作模式,如下图所示:

当一个异常发生时,将切换进入相应的工作模式,这是ARM920T CPU将自动完成如下工作:

①在异常工作模式的连接寄存器R14中保存前一个工作模式的下一条即将执行的指令地址。对于ARM状态,这个值是当前PC值加4或加8

②将CPSR的值复制到异常模式的SPSR

③将CPSR的工作模式位设为这个异常对应的工作模式

④令PC值等于这个异常模式在异常向量表中的地址,即跳转去执行异常向量表中的相应指令

从异常工作模式回到之前的工作模式时,需要通过软件完成如下事情:

①前面进入异常工作模式时,连接寄存器中保存了前一工作模式的一个指令地址,将它减去适当的值后赋值给PC寄存器

②将SPSR的复制回CPSR

| 异常模式 | 退出异常模式时PC的计算方法 | 进入异常模式时R14中保存的值 |

| 管理模式(SWI指令进入) | MOVS PC, R14 | PC+4(1) |

| 未定义指令终止模式 | MOVS PC, R14 | PC+4(1) |

| 快速中断模式 | SUBS PC, R14, #4 | PC+4(2) |

| 中断模式 | SUBS PC, R14, #4 | PC+4(2) |

| 数据访问终止模式 | 异常原因:指令预取终止 SUBS PC, R14, #4 | PC+4(1) |

异常原因:数据访问终止 SUBS PC, R14, #8 | PC+8(3) |

注:

(1)PC为这些指令的地址:SWI、未定义的指令、在预取指时就失败的指令

(2)PC为这些指令的地址:进入快速中断模式、中断模式前,被打断而未执行的指令

(3)PC为这些指令的地址:导致数据访问终止的加载/存储指令(LDR、STR、LDM和STM)

二、S3C2440中断控制器

当某事件发生时,硬件会设置某个寄存器,CPU在执行完一个指令时,通过硬件查看这个寄存器,如果发现所关注的事件发生了,则中断当前程序流程,跳转到一个固定的地址处理这个事件,最后返回继续执行被中断的程序。

中断处理的过程:

①中断控制器汇集各类外设发出的中断信号,告诉CPU

②CPU保存当前程序的运行环境,调用中断服务程序(ISR)来处理这些中断

③在ISR中通过读取中断控制器、外设的相关寄存器来识别时哪个中断,并进行相应处理

④清除中断:通过读写中断控制器和外设的相关寄存器来实现

⑤最后恢复被中断程序的运行环境(恢复寄存器),继续执行

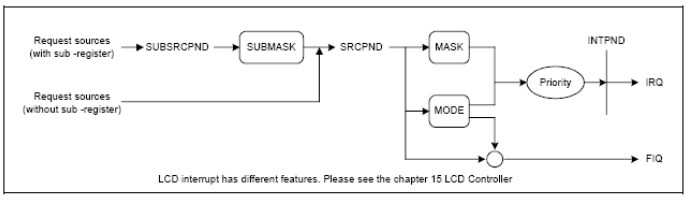

s3c2440的中断控制器结构如上图所示:

①request sources(without sub-register)中的中断源被触发后,SRCPND寄存器中相应位被置1,如果此中断没有被INTMSK寄存器屏蔽或者快速中断的话,它将被进一步处理。

② 对于request sources(with sub-register)中的中断源被触发后,SUBSRCPEND寄存器中的相应位被置1,如果此中断没有被INTSUBMSK寄存器屏蔽的话,它在 SRCPND寄存器中的相应位也被置1,以后的处理过程就和①步骤类似。

③如果被触发的中断中有快速中断,INTMOD寄存器中为1的位对应的中断是FIQ,则CPU进入快速中断模式进行处理

④ 对于一般的中

S3C2440中断体系结 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)