从实践角度探讨高速PCB的布线问题

εr表示PCB材料的相对磁导率。T表示PCB的厚度。D1表示环绕通孔的焊盘直径。D2表示接地平面中隔离孔的直径。所有尺寸均以cm为单位。在一块0.157 cm厚的PCB上一个通孔就可以增加1.2 nH的寄生电感和0.5 pF的寄生电容;这就是为什么在给PCB布线时一定要时刻保持戒备的原因,要将寄生效应的影响降至最校

接地平面

实际上需要讨论的内容远不止本文提到的这些,但是我们会重点突出一些关键特性并鼓励读者进一步探讨这个题。本文的最后列出有关的参考文献。

接地平面起到公共基准电压的作用,提供屏蔽,能够散热和减小寄生电感(但它也会增加寄生电容)的功能。虽然使用接地平面有许多好处,但是在实现时也必须小心,因为它对能够做的和不能够做的都有一些限制。

理想情况下,PCB有一层应该专门用作接地平面。这样当整个平面不被破坏时才会产生最好的结果。千万不要挪用此专用层中接地平面的区域用于连接其它信号。由于接地平面可以消除导体和接地平面之间的磁场,所以可以减小印制线电感。如果破坏接地平面的某个区域,会给接地平面上面或下面的印制线引入意想不到的寄生电感。

因为接地平面通常具有很大的表面积和横截面积,所以使接地平面的电阻保持最小值。在低频段,电流会选择电阻最小的路径,但是在高频段,电流会选择阻抗最小的路径。

然而也有例外,有时候小的接地平面会更好。如果将接地平面从输入或者输出焊盘下挪开,高速运算放大器会更好地工作。因为在输入端的接地平面引入的寄生电容,增加了运算放大器的输入电容,减小了相位裕量,从而造成不稳定性。正如在寄生效应一节的讨论中所看到的,运算放大器输入端1 pF的电容能引起很明显的尖脉冲。输出端的容性负载——包括寄生的容性负载——造成了反馈环路中的极点。这会降低相位裕量并造成电路变得不稳定。

如果有可能的话,模拟电路和数字电路——包括各自的地和接地平面——应该分开。快速的上升沿会造成电流毛刺流入接地平面。这些快速的电流毛刺引起的噪声会破坏模拟性能。模拟地和数字地(以及电源)应该被连接到一个共用的接地点以便降低循环流动的数字和模拟接地电流和噪声。

在高频段,必须考虑一种称为"趋肤效应"的现象。趋肤效应会引起电流流向导线的外表面——结果会使得导线的横截面变窄,因此使直流(DC)电阻增大。虽然趋肤效应超出了本文讨论的范围,这里还是给出铜线中趋肤深度(Skin Depth)的一个很好的近似公式(以cm为单位): (5)

(5)

低灵敏度的电镀金属有助于减小趋肤效应。

封装

运算放大器通常采用不同的封装形式。所选的封装会影响放大器的高频性能。主要的影响包括寄生效应(前面提到的)和信号路径。这里我们集中讨论放大器的路径输入、输出和电源。

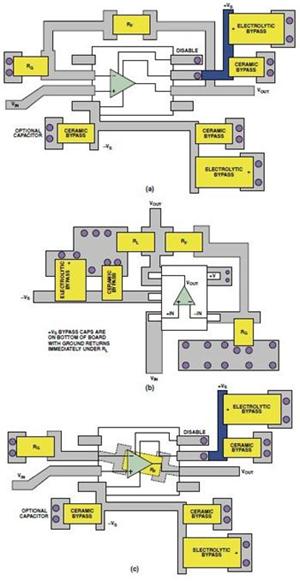

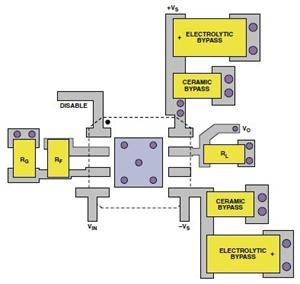

图9示出了采用SOIC封装(a)和SOT-23封装(b)的运算放大器之间的布线区别。每种封装都有它自身的一些问题。重点看(a),仔细观察反馈路径就发现有多种方法连接反馈。最重要的是保证印制线长度最短。反馈路径中的寄生电感会引起振铃和过冲。在图9(a)和9(b)中,环绕放大器连接反馈路径。图9(c)示出了另外一种方法——在SOIC封装下面连接反馈路径——这样就减小了反馈路径的长度。每种方法都有细微的差别。第一种方法会导致印制线过长,会增大串联电感。第二种方法采用了通孔,会引起寄生电容和寄生电感。在给PCB布线时必须要考虑这些寄生效应的影响及其隐含的问题。SOT-23布线差几乎是最理想的:反馈印制线长度最短,而且很少利用通孔;负载和旁路电容从很短的路径返回到相同的地线连接;正电源端的电容(图9(b)中未示出)直接放在在PCB的背面的负电源电容的下面。

图9. 同一运算放大器电路的布线区别。(a)SOIC封装,(b)SOT-23封装,(c)在PCB下面采用RF的SOIC封装。

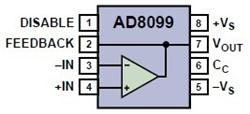

低失真放大器的引脚排列:ADI公司提供的一些运算放大器(例如AD80451)采用了一种新的低失真引脚排列,有助于消除上面提及的两个问题;而且它还提高了其它两个重要方面的性能。LFCSP的低失真引脚排列,如图10所示,将传统运算放大器的引脚排列按着逆时针方向移动一个引脚并且增加了一个输出引脚作为专用的反馈引脚。

图10. 采用低失真引脚排列的运算放大器。

低失真引脚排列允许输出引脚(专用反馈引脚)和反相输入引脚之间可以靠近连接,如图11所示。这样极大地简化和改善了布线。

图11. AD8045低失真运算放大器的PCB布线。

这种引脚排列还有一个好处就是降低了二次谐波失真。传统运算放

- PCB布线规则详解(12-02)

- PCB布线原则(11-28)

- 优化PCB布线减少串扰的解决方案(08-09)