ARM裸机开发bootloader核心初始化

是Cache

我们都知道处理器的访问速度是非常快的,而内存的速度却慢的很。这样当处理器在访问内存时就出现了问题。而Cache恰恰就用来解决这个问题。从物理结构上来讲,Cache位于处理器与内存之间,cache中存储了处理器经常从内存访问的数据与指令,也就是cache是内存的部分拷贝。这时处理器往往先访问cache,如果cache中没有想要的数据,才去内存查找。而cache的访问速度要比内存大的多,这样就提高了整个的运行效率。

cache又分为:I-Cache和D-Cache

3、MMU

谈到MMU这个时候就要先说一下虚拟地址:作为一个程序员,大家都知道有逻辑地址和物理地址之分,如果我们不直接和硬件打交道,我们根本不用去管物理地址,只要用逻辑地址就可以了。而MMU就是把逻辑地址转换为物理地址的协议。

假如我们只使用物理地址就会出现两个问题要解决:1、地址冲突(两段程序使用同一物理地址)。2、范围小

我们使用了MMU就可以把逻辑地址映射到物理地址,再具体的说就是两段程序使用的是同一逻辑地址,而经过映射后,它们都被映射到不同的物理地址。还有就是地址空间变大了。具体的物理地址的分配不用程序员来管,都要MMU来分配,这样就可以更好的利用物理空间。

ARM11之间Cache位于MMU前面靠近处理器,也就是说cache使用的是虚拟地址(逻辑地址),而ARM11之后包括ARM11的MMU靠近内存,这个时候使用的是物理地址。

4、为什么要关闭MMU和Cache

MMU和Cache在使用之前要进行配置,在ARM初始化的时候还没有进行配置,所以这个时候要关闭它们。还有就是避免Bootloader将linux内核下载到D-cache中,而I-cache这个时候可以不管它。

关闭MMU和Cache的步骤:

1、使I-cache和D-cache失效

2、关闭I-Cache和D-Cache,关闭MMU

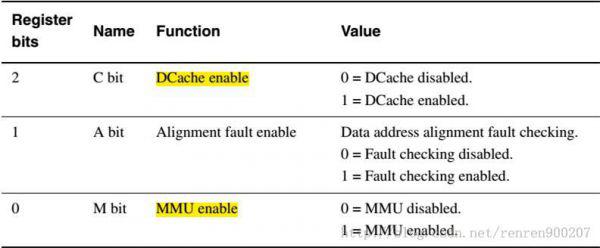

下面是cp15的寄存器解释:

代码如下:

disable_mmu:

mcr p15, 0, r0, c7, c7, 0

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #0x00000007

mcr p15, 0, r0, c1, c0, 0

2440、6410和210的cp15是一样的。所以这里的代码也是一样的。

整个核心初始化的代码为:

.text.global _start_start:b resetldr pc, _undefined_instructionldr pc, _software_interruptldr pc, _prefetch_abortldr pc, _data_abortldr pc, _irqldr pc, _fiq_undefined_instruction: .word undefined_instruction_software_interrupt: .word software_interrupt_prefetch_abort: .word prefetch_abort_data_abort: .word data_abort_not_used: .word not_used_irq: .word irq_fiq: .word fiqundefined_instruction:nopsoftware_interrupt:nopprefetch_abort:nopdata_abort:nopnot_used:nopirq:nopfiq:nopreset:bl set_svcbl disable_watchdogbl disable_interruptbl disable_mmuset_svc:mrs r0, cpsrbic r0, r0, #0x1forr r0, r0, #0xd3msr cpsr, r0mov pc, lr#define pWTCON 0x7E004000disable_watchdog:ldr r0, =pWTCON /*mov的操作数最多为8位*/mov r1, #0x0str r1, [r0]mov pc, lrdisable_interrupt:mvn r1, #0x0ldr r0, =0x71200014str r1, [r0]ldr r0, =0x71300014str r1, [r0]mov pc, lrdisable_mmu:mcr p15, 0, r0, c7, c7, 0mrc p15, 0, r0, c1, c0, 0bic r0, r0, #0x00000007mcr p15, 0, r0, c1, c0, 0mov pc, lr

ARM裸机开发bootloader核心初始 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)