S3C6410 时钟初始化

时间:11-20

来源:互联网

点击:

1.PHASE LOCKED LOOP(PLL)

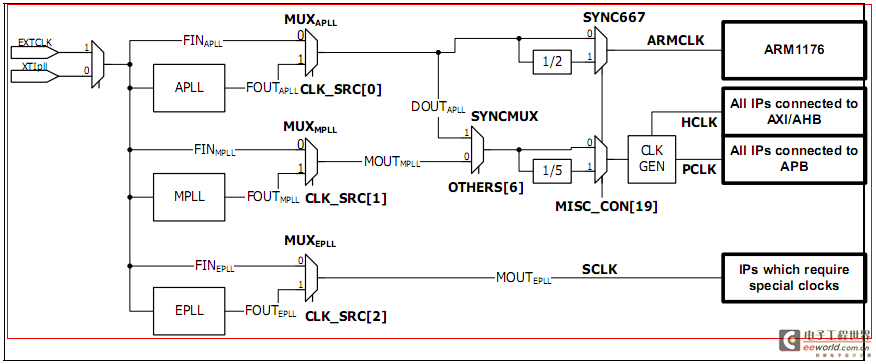

S3C6410里包含三个PLL(锁相环),APLL, MPLL, EPLL,通过设置它们将输入时钟同步输出达到操作CPU的工作频率的目的。如图1-1所示。

Voltage Controlled Oscillator (VCO)P[5:0]位来设置FIN进行分频。通过设置Main-Divider分频数,分频压控振荡器产生的输出时钟频率,分频之后的低频进入鉴相器ScalerS[2:0]位设置PLL的输出时钟频率都可以通过

PLL的时钟选择和输入参照时钟

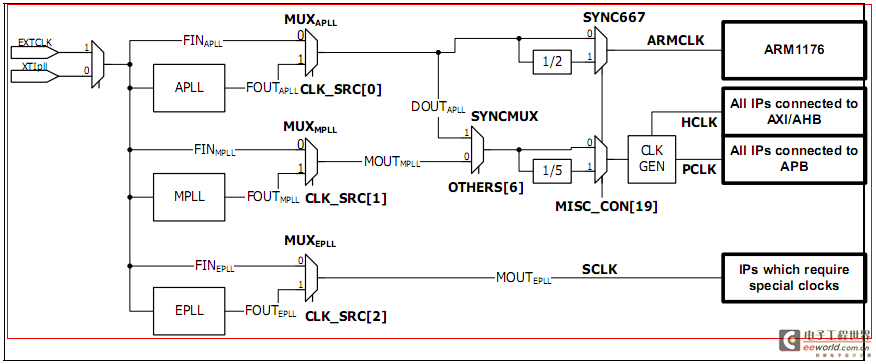

图1-2描述了时钟产生逻辑。S3C6410有三个PLL锁相环,工作时钟也分为三组,APLL用来为ARM芯片提供工作时钟,MPLL为AXI,AHB,APB总线上设备提供工作时钟,EPLL为特殊外设,如:视频解码器,图片编码器等,提供工作时钟。

图1-2时钟产生逻辑单元

CLK_SRC寄存器的低三位CLK_SRC[2:0]分别控制三种工作时钟。当对应位被置位,则产生对应PLL的工作时钟。否则,不会产生对应的PLL工作时钟。

3.三种工作时钟的产生

ARM1176最高产生667Mhz的工作频率。用户可以通过设置内部时钟分频器的值来控制输出工作时钟,而不用修改PLL的工作频率。分频器可以选择1~16的分频数。ARM内核可以通过修改分频器的值来减少系统电源的损耗。

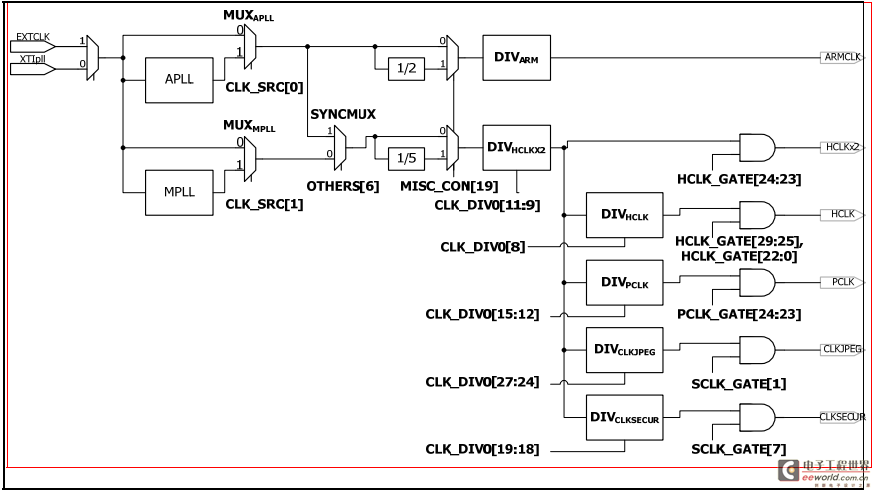

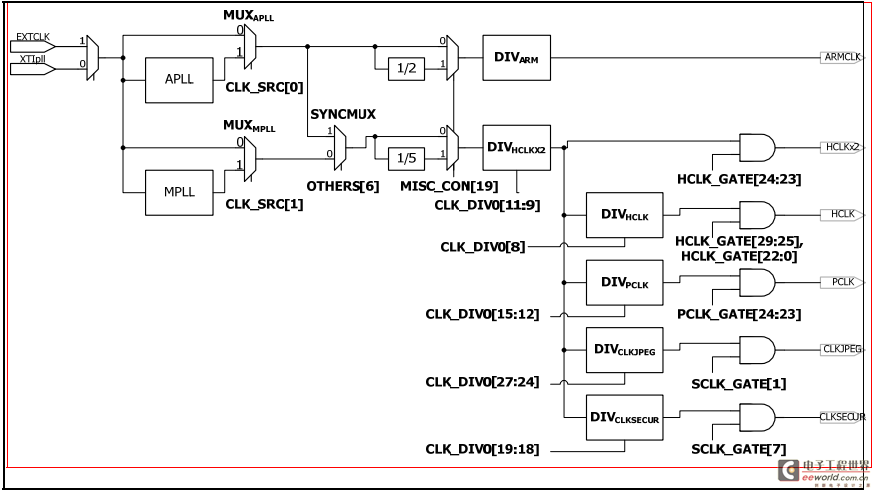

S3C6410内部含有AXI,AHB和APB总线,通过不同的总线控制不同的外设,关闭总线上的时钟频率可以达到系统节能的目的。AXI,AHB总线最高工作在133MHz频率下,APB总线最高工作在66MHz频率下。由于APB和AXI,AHB总线上二者工作频率不一致,在这两种总线上进行数据同步传输时会采用特殊逻辑单元,如图1-3所示。

图1-3系统总线工作频率设置

HCLKX2时钟由DDR0,DDR1两个DDR控制器产生,其最高可以以266MHz频率发送和接收数据。每个HCLKX2时钟可以根据用户需要分别被关闭掉来减少系统损耗。AHB总线上的时钟由div(HCLK)分频器分频后输出,同样AHB总线上的外设也可以被关闭掉以节省电源消耗。HCLK_GATE寄存器用来关闭工作在HCLKX2和HCLK时钟上的外设。

慢速设备连接在APB总线上。APB时钟最高工作在66MHz,通过div(PCLk)分频器来进行分频设置,通过设置PCLK_GATE寄存器来关闭对应的APB总线上的外设。根据S3C6410硬件手册说明,AHB总线和APB总线上的频率必须是偶数,例如,如果div(HCLK)对应控制位CLK_div[8]设置为1,则div(PCLK)对应位CLK_div0[15:12]必须设置为1,3,5,…等奇数。否则,APB总线上的外设不能正解的进行数据传输。

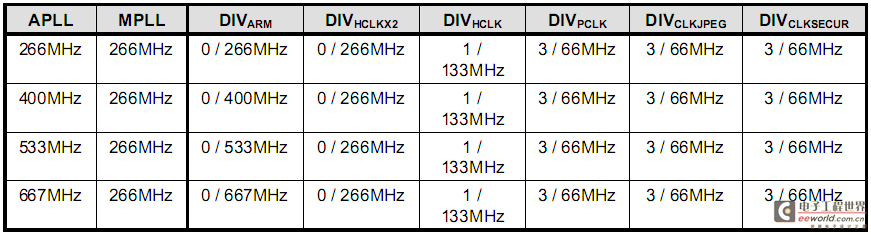

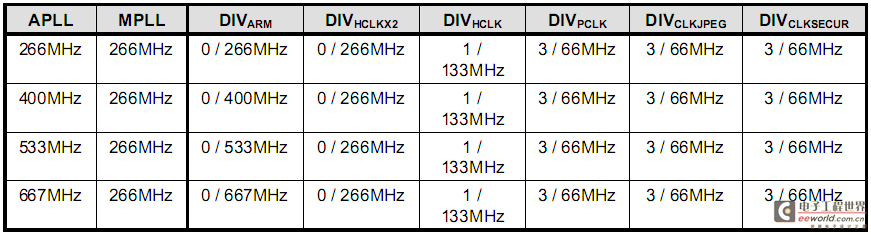

AHB总线上的JPEG和安全相关子系统不能工作在133MHz,AHB总线专门为这样低频子系统提供低频工作时钟,通过设置div(CLKJPEG)和div(CLKSECUR)分频位来设置其工作频率。因此,同样在APB总线上也有类似的这种限制设定,div(CLKJPEG)和div(CLKSECUR)对应的CLK_div0[27:24]分频位和CLK_div0[19:18]分频位必须是奇数,二者的和是偶数。如表1-1所示,官方给出了推荐的设置参数。

表1-1官方推荐参数

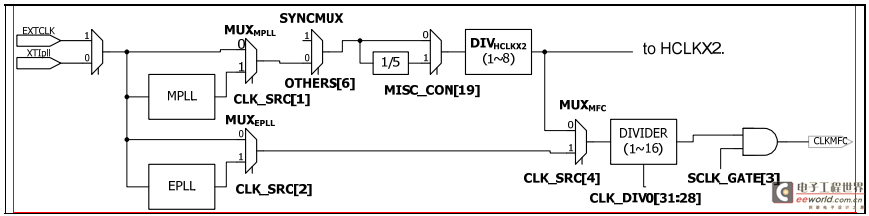

4.MFC模块时钟的产生

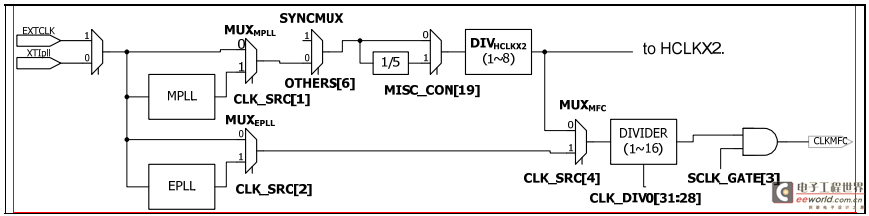

MFC模块需要特殊的时钟,如图1-5所示。

图1-5 MFC时钟产生逻辑

MFC时钟源可以从HCLKX2和MOUT(EPLL)中选择。MFC的工作时钟使用HCLKX2来分频。默认HCLKX2时钟频率为266MHz。因此,CLK_div0[31:28]必须设置为b0001来产生MFC工作的133MH时钟。当MFC模块不需要工作在高性能模式下时,有两种方式可以减少MFC模块工作频率来达到减少MFC模块的功耗。第一种方式是设置CLK_SRC[4]使用EPLL的输出时钟,另外一种方式是设置CLK_div0[31:28]的分频数,同时,设置CLK_SRC[4]位,这样低频工作时钟就可以提供给MFC模块。EPLL输出时钟是与HCLKX2和HCLK独立的。

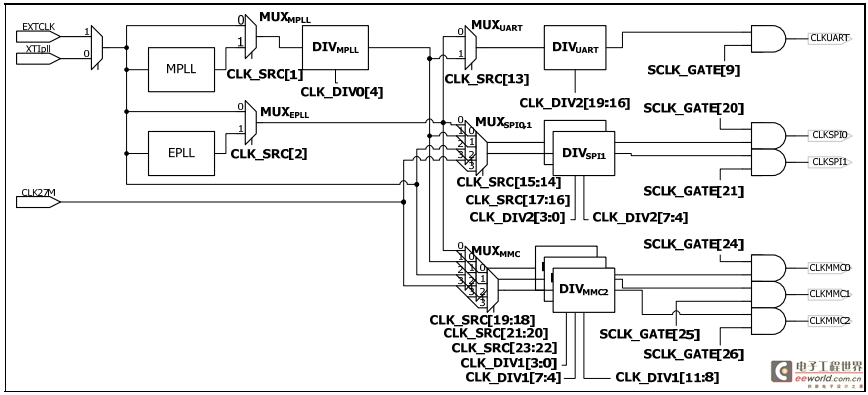

5.UART,SPI,MMC工作时钟的产生

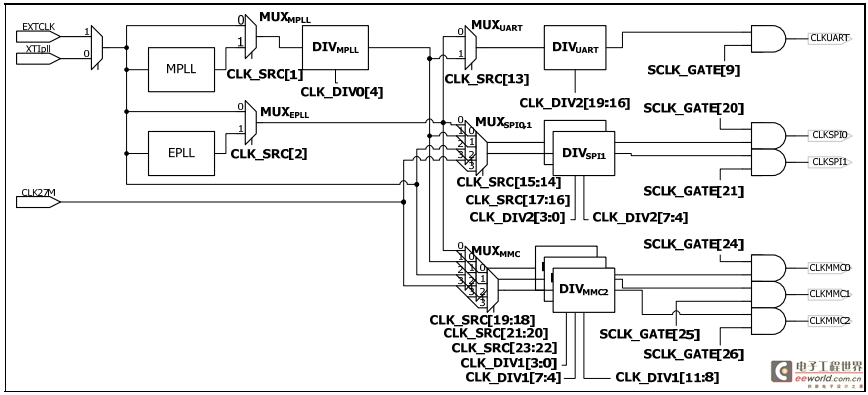

如图1-6所示,是上述三种外设工作时钟逻辑。

图1-6 UART,SPI,MMC工作时钟逻辑模块

通过设置CLK_div2[19:16]位来设置UART的工作频率的分频数,通过SCLK_GATE[9]来开启关闭UART时钟源。

该模块中有一个额外的时钟源CLK27M,使用该时钟源可以提供更多的可选工作时钟。

6.时钟的开启/关闭控制

HCLK_GATE,PCLK_GATE和SCLK_GATE用来控制三种时钟源的产生,如果对应的位被设置,对应时钟就会产生。

HCLK_GATE控制HCLK总线上的外设工作时钟的产生,PCLK_GATE控制PCLK总线上的外设工作时钟的产生,PCLK总线上的外设需要特定的时钟,它们通过SCLK_GATE来设置。

7.同步667MH操作模式

根据S3C6410硬件手册,ARMCLK和HCLK的时钟比必须是整数,用来同步ARM内核和AXI总线接口二者的时钟。S3C6410没有对CPU工作在533MHz做限制,ARMCLK = 533MHz,HCLKX2=266MHz,HCLK=133MH,不过,对于工作在533MHz以上时,例如667Mhz时,只能支持1:2.5:5的时钟比(ARMCLK = 667MHz,HCLKX2=266MHz,HCLK=133MH)

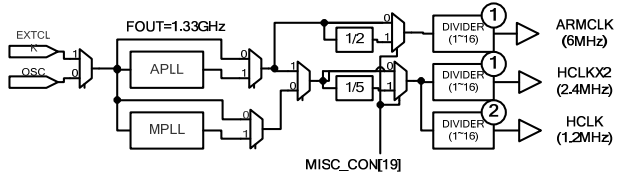

8.时钟分频

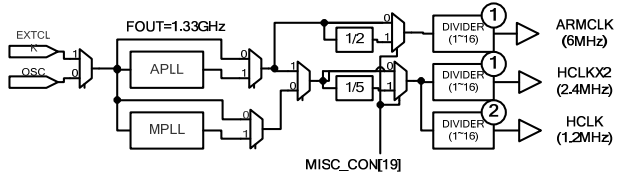

图1-7时钟分频模块

如图1-7所示,时钟分频模块产生三种时钟,ARMCLK,HCLKX2,HCLK。时钟分频器包含两部分,预分频器组和后分频器组,预分频器包含一个1/2预分频器和1/5预分频器,这两个分频器是固定的不能被软件配置,而后分频器可以通过配置CLK_div0寄存器方式进行配置。当MISC_CON的SYNC667MHz位被设置时,两个预分频器同时工作,产生APLL的分频经过预分频器分频的时钟,如果APLL的FOUT输出频率为1.33GHz,预分频器ARMCLK的输出为667Mhz,预分频器HCLK的输出为266MHz。这样经过分频的时钟可以通过CLK_div0寄存器进行配置。

我们打算将ARM内核时钟设置为官方推荐的稳定的533MHz,让APLL为AHB,APB输出工作频率。让MPLL为UART等外设提供工作频率,EPLL不工作。同时设置HCLKX2为266MHz,HCLK为133MHz,PCLK为66.5MHz,UART工作时钟为66.5MHz。

1.选择HCLKX2, HCLK, PCLK的时钟源,由图1-2可知其时钟源可以通过OTHER[6]选择是由DOUT_APLL还是MOUT_MPLL,我们选择从DOUT_APLL。

S3C6410里包含三个PLL(锁相环),APLL, MPLL, EPLL,通过设置它们将输入时钟同步输出达到操作CPU的工作频率的目的。如图1-1所示。

Voltage Controlled Oscillator (VCO)P[5:0]位来设置FIN进行分频。通过设置Main-Divider分频数,分频压控振荡器产生的输出时钟频率,分频之后的低频进入鉴相器ScalerS[2:0]位设置PLL的输出时钟频率都可以通过

PLL的时钟选择和输入参照时钟

图1-2描述了时钟产生逻辑。S3C6410有三个PLL锁相环,工作时钟也分为三组,APLL用来为ARM芯片提供工作时钟,MPLL为AXI,AHB,APB总线上设备提供工作时钟,EPLL为特殊外设,如:视频解码器,图片编码器等,提供工作时钟。

图1-2时钟产生逻辑单元

CLK_SRC寄存器的低三位CLK_SRC[2:0]分别控制三种工作时钟。当对应位被置位,则产生对应PLL的工作时钟。否则,不会产生对应的PLL工作时钟。

3.三种工作时钟的产生

ARM1176最高产生667Mhz的工作频率。用户可以通过设置内部时钟分频器的值来控制输出工作时钟,而不用修改PLL的工作频率。分频器可以选择1~16的分频数。ARM内核可以通过修改分频器的值来减少系统电源的损耗。

S3C6410内部含有AXI,AHB和APB总线,通过不同的总线控制不同的外设,关闭总线上的时钟频率可以达到系统节能的目的。AXI,AHB总线最高工作在133MHz频率下,APB总线最高工作在66MHz频率下。由于APB和AXI,AHB总线上二者工作频率不一致,在这两种总线上进行数据同步传输时会采用特殊逻辑单元,如图1-3所示。

图1-3系统总线工作频率设置

HCLKX2时钟由DDR0,DDR1两个DDR控制器产生,其最高可以以266MHz频率发送和接收数据。每个HCLKX2时钟可以根据用户需要分别被关闭掉来减少系统损耗。AHB总线上的时钟由div(HCLK)分频器分频后输出,同样AHB总线上的外设也可以被关闭掉以节省电源消耗。HCLK_GATE寄存器用来关闭工作在HCLKX2和HCLK时钟上的外设。

慢速设备连接在APB总线上。APB时钟最高工作在66MHz,通过div(PCLk)分频器来进行分频设置,通过设置PCLK_GATE寄存器来关闭对应的APB总线上的外设。根据S3C6410硬件手册说明,AHB总线和APB总线上的频率必须是偶数,例如,如果div(HCLK)对应控制位CLK_div[8]设置为1,则div(PCLK)对应位CLK_div0[15:12]必须设置为1,3,5,…等奇数。否则,APB总线上的外设不能正解的进行数据传输。

AHB总线上的JPEG和安全相关子系统不能工作在133MHz,AHB总线专门为这样低频子系统提供低频工作时钟,通过设置div(CLKJPEG)和div(CLKSECUR)分频位来设置其工作频率。因此,同样在APB总线上也有类似的这种限制设定,div(CLKJPEG)和div(CLKSECUR)对应的CLK_div0[27:24]分频位和CLK_div0[19:18]分频位必须是奇数,二者的和是偶数。如表1-1所示,官方给出了推荐的设置参数。

表1-1官方推荐参数

4.MFC模块时钟的产生

MFC模块需要特殊的时钟,如图1-5所示。

图1-5 MFC时钟产生逻辑

MFC时钟源可以从HCLKX2和MOUT(EPLL)中选择。MFC的工作时钟使用HCLKX2来分频。默认HCLKX2时钟频率为266MHz。因此,CLK_div0[31:28]必须设置为b0001来产生MFC工作的133MH时钟。当MFC模块不需要工作在高性能模式下时,有两种方式可以减少MFC模块工作频率来达到减少MFC模块的功耗。第一种方式是设置CLK_SRC[4]使用EPLL的输出时钟,另外一种方式是设置CLK_div0[31:28]的分频数,同时,设置CLK_SRC[4]位,这样低频工作时钟就可以提供给MFC模块。EPLL输出时钟是与HCLKX2和HCLK独立的。

5.UART,SPI,MMC工作时钟的产生

如图1-6所示,是上述三种外设工作时钟逻辑。

图1-6 UART,SPI,MMC工作时钟逻辑模块

通过设置CLK_div2[19:16]位来设置UART的工作频率的分频数,通过SCLK_GATE[9]来开启关闭UART时钟源。

该模块中有一个额外的时钟源CLK27M,使用该时钟源可以提供更多的可选工作时钟。

6.时钟的开启/关闭控制

HCLK_GATE,PCLK_GATE和SCLK_GATE用来控制三种时钟源的产生,如果对应的位被设置,对应时钟就会产生。

HCLK_GATE控制HCLK总线上的外设工作时钟的产生,PCLK_GATE控制PCLK总线上的外设工作时钟的产生,PCLK总线上的外设需要特定的时钟,它们通过SCLK_GATE来设置。

7.同步667MH操作模式

根据S3C6410硬件手册,ARMCLK和HCLK的时钟比必须是整数,用来同步ARM内核和AXI总线接口二者的时钟。S3C6410没有对CPU工作在533MHz做限制,ARMCLK = 533MHz,HCLKX2=266MHz,HCLK=133MH,不过,对于工作在533MHz以上时,例如667Mhz时,只能支持1:2.5:5的时钟比(ARMCLK = 667MHz,HCLKX2=266MHz,HCLK=133MH)

8.时钟分频

图1-7时钟分频模块

如图1-7所示,时钟分频模块产生三种时钟,ARMCLK,HCLKX2,HCLK。时钟分频器包含两部分,预分频器组和后分频器组,预分频器包含一个1/2预分频器和1/5预分频器,这两个分频器是固定的不能被软件配置,而后分频器可以通过配置CLK_div0寄存器方式进行配置。当MISC_CON的SYNC667MHz位被设置时,两个预分频器同时工作,产生APLL的分频经过预分频器分频的时钟,如果APLL的FOUT输出频率为1.33GHz,预分频器ARMCLK的输出为667Mhz,预分频器HCLK的输出为266MHz。这样经过分频的时钟可以通过CLK_div0寄存器进行配置。

我们打算将ARM内核时钟设置为官方推荐的稳定的533MHz,让APLL为AHB,APB输出工作频率。让MPLL为UART等外设提供工作频率,EPLL不工作。同时设置HCLKX2为266MHz,HCLK为133MHz,PCLK为66.5MHz,UART工作时钟为66.5MHz。

1.选择HCLKX2, HCLK, PCLK的时钟源,由图1-2可知其时钟源可以通过OTHER[6]选择是由DOUT_APLL还是MOUT_MPLL,我们选择从DOUT_APLL。

S3C6410时钟初始 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)