ARM协处理器CP15寄存器详解

31 |

(四)CP15

CP15

31 | |||||||||||||||

D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

在

00:当前级别下,该内存区域不允许被访问,任何的访问都会引起一个domain fault,这时 AP位无效

01:当前级别下,该内存区域的访问必须配合该内存区域的段描述符中AP位进行权检查

10:保留状态(我们最好不要填写该值,以免引起不能确定的问题)

11:当前级别下,对该内存区域的访问都不进行权限检查。

所以只有当相应域的编码为 01

(五)CP15

CP15

MRC p15, 0, , c5, c0, 0 访问数据失效状态寄存器

MRC p15, 0, , c5, c0, 1访问指令状态失效寄存器

编码格式如下所示:

31 | 8 | 7 | 3 |

UNP/SBZP | 0 | 域标识 | 状态标识 |

其中,域标识bit[7:4]表示存放引起存储访问失效的存储访问所属的域。状态标识bit[3:0] 表示放引起存储访问失效的存储访问类型,该字段含义如下表所示(优先级由上到下递减)。

引起访问失效的原因 | 状态标识 | 域标识 | C6 |

终端异常( | 0b0010 | 无 效 | 生 产商定义 |

中断向量访问异常( | 0b0000 | 无 效 | 有 效 |

地 址对齐 | 0b00x1 | 无 效 | 有 效 |

一 级页表访问失效 | 0b1100 | 无 效 | 有 效 |

二 级页表访问失效 | 0b1110 | 有 效 | 有 效 |

基 于段的地址变换失效 | 0b0101 | 无 效 | 有 效 |

基 于页的地址变换失效 | 0b0111 | 有 效 | 有 效 |

基 于段的存储访问中域控制失效 | 0b1001 | 有 效 | 有 效 |

基 于页的存储访问中域控制失效 | 0b1101 | 有 效 | 有 效 |

基 于段的存储访问中访问权限控制失效 | 0b1111 | 有 效 | 有 效 |

基 于页的存储访问中访问权限控制失效 | 0b0100 | 有 效 | 有 效 |

基于段的 | 0b0110 | 有 效 | 有 效 |

基于页的 | 0b1000 | 有 效 | 有 效 |

基于段的非 | 0b1010 | 有 效 | 有 效 |

(六)CP15的寄存器C6

CP15

MRC p15, 0, , c6, c0, 0访问数据失效地址寄存器

MRC p15, 0, , c6, c0, 2 访问指令失效地址寄存器

编码格式如下所示:

31 |

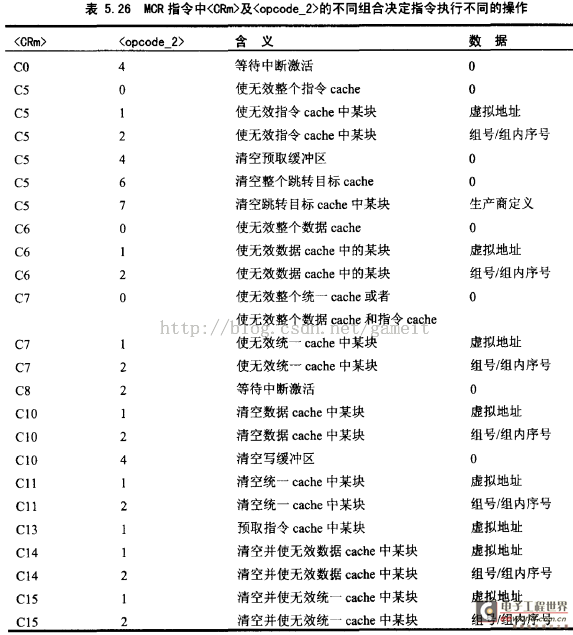

(七)CP15的寄存器C7

CP15

访问

mcr p15, 0, , , crm,

表中的数据是指Rd中的数据:

(八)CP15的寄存器C8

指令 | Rd | 含义 |

MCR p15, 0, Rd, c8, c5, 0 | 0 | 使无效整个指令TLB |

MCR p15, 0, Rd, c8, c5, 1 | 虚拟地址 | 使无效指令TLB中的单个地址变换条目 |

MCR p15, 0, Rd, c8, c6, 0 | 0 | 使无效整个数据TLB |

MCR p15, 0, Rd, c8, c6, 1 | 虚拟地址 | 使无效数据TLB中的单个地址变换条目 |

MCR p15, 0, , c8, c7, 0 | 0 | 使无效整个数据和指令TLB |

MCR p15, 0, , c8, c7, 1 | 虚拟地址 | 使无效数据和指令TLB中的单个地址变换条目 |

(九)CP15的寄存器C12

CP15寄存器C12用来设置异常向量基地址,其编码格式如下所示:

MCR p15, 0, , c12, c0, 0 ;Rd中存放要修改的异常向量基地址

31 | 4 |

异常向量基地址 | Reserve |

注:只有ARM11和cortex-a 可以任意修改异常向量基地址。arm7,ARM9,ARM10只可以在0地址或0xffff0000中

(十)CP15的寄存器C13

CP15中的寄存器C13用于快速上下文切换。其编码格式如下所示。

访问寄存器C13的指令格式如下所示。

MCR

MRC

其中,在读操作时,结果中位[31::25]返回PID,其他位 的数值是不可以预知的。写操作将设置PID的值。

ARM协处理器CP15寄存 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)