I2C总线学习终结,开始SPI总线的学习

时间:11-22

来源:互联网

点击:

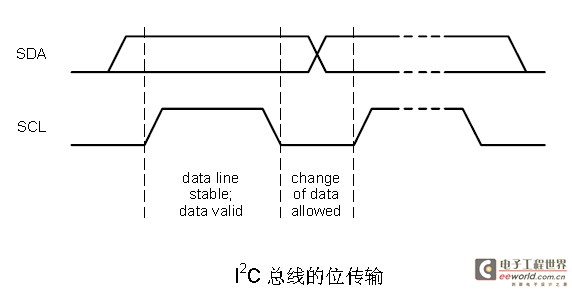

学习IIC总线近一个星期了,由浅及深,慢慢的理解了很多的东西。但一直对IIC总线协议的总线时序不甚理解。对数据位的传送,懵懵懂懂,知其然,不知其所以然。查看了很多的资料,都是这样描述数据位的传输:在I2C总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。进行数据传送时,在SCL呈现高电平期间,SDA上的电平必须保持稳定,低电平为数据0,高电平为数据1。只有在SCL为低电平期间,才允许SDA上的电平改变状态。尤其对“进行数据传送时,在SCL呈现高电平期间,SDA上的电平必须保持稳定,低电平为数据0,高电平为数据1。只有在SCL为低电平期间,才允许SDA上的电平改变状态”这句话不甚理解。

带着这个问题,我在图书馆找了好几天的资料。终于弄懂了。

每bit数据定义

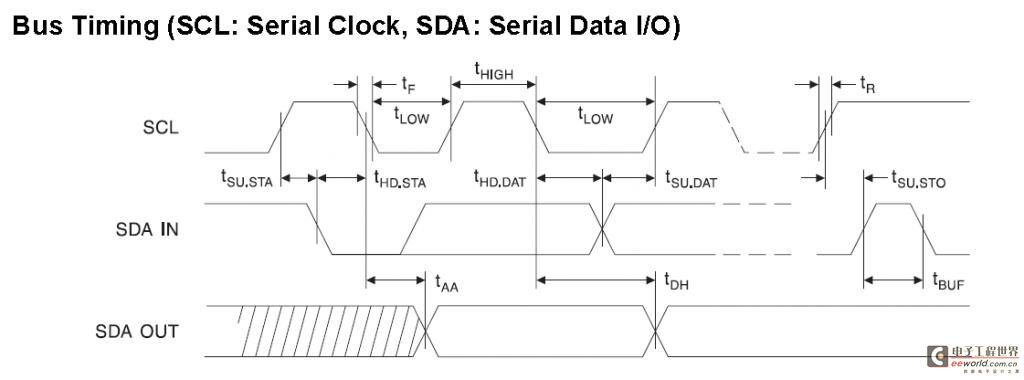

下面再来看一下IIC总线时序的具体定义:

其中, 是数据建立的时间;

是数据建立的时间; 是数据保持时间。上升沿将数据送到SDA线上,

是数据保持时间。上升沿将数据送到SDA线上, 是建立时间。高电平期间数据稳定,等待下降沿读取SDA线上的数据。下降沿从SDA线上读取数据,下降沿之后的

是建立时间。高电平期间数据稳定,等待下降沿读取SDA线上的数据。下降沿从SDA线上读取数据,下降沿之后的 是保持时间。

是保持时间。

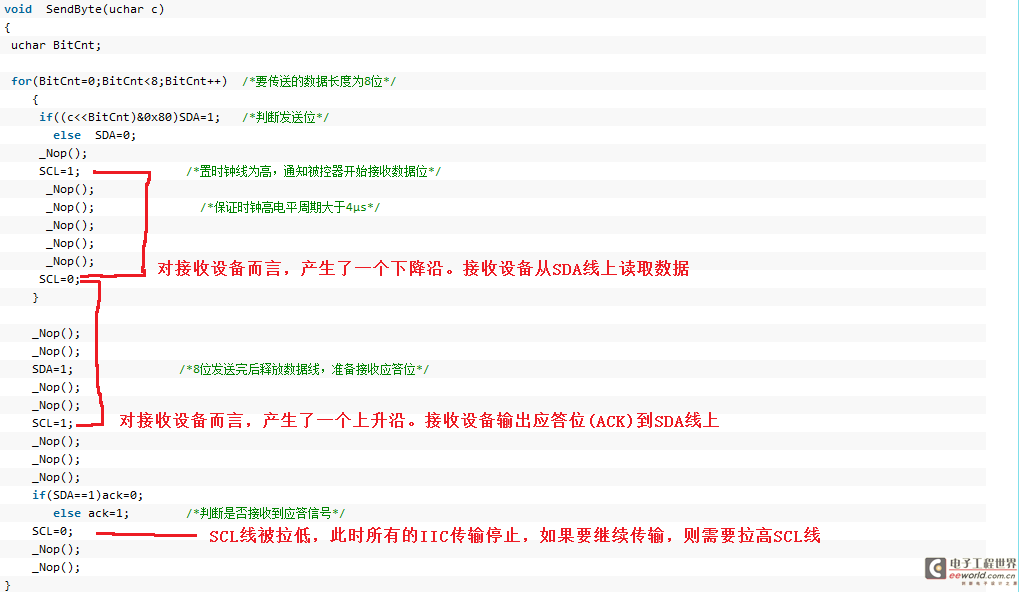

下面是发送数据的时序变化具体分析。

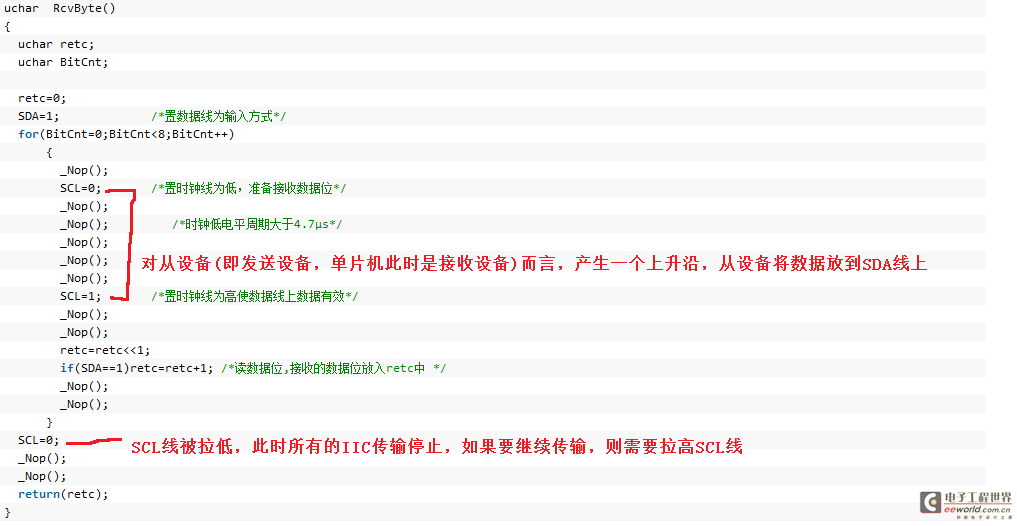

再来看一下接收数据时的时序的变化。

IIC总线协议的学习暂告一段落,开始SPI总线的学习!

I2C总线SPI总 相关文章:

- 比较流行的几种内部总线技术(12-15)

- I2C总线和SPI总线调试简介(12-14)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)