ARM MMU工作原理剖析

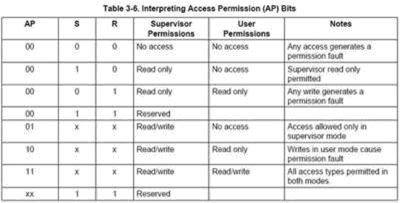

AP位也是有四个值,我结合实例对其进行说明.

在下面的例子中,我们的DOMAIN ACCESS CONTROL REGISTER都被初始化成0xFFFF BDCF,如下图所示:

例1:

Discriptor 中的domain=4,AP=10(这种情况下S bit ,A bit 被忽略)

假设现在我要对该描述符描述的内存区域进行访问:

由于domain=4,而DOMAIN ACCESS CONTROL REGISTER中field 4的值是01,系统会对该访问进行访问权限的检查。

假设当前CPU处于Supervisor模式下,则程序可以对该描述符描述的内存区域进行读写操作。

假设当前CPU处于User模式下,则程序可以对该描述符描述的内存进行读访问,若对其进行写操作则引起一个permission fault.

例2:

Discriptor 中的domain=0,AP=10(这种情况下S bit ,A bit 被忽略)

domain=0,而DOMAIN ACCESS CONTROL REGISTER中field 0的值是11,系统对任何内存区域的访问都不进行访问权限的检查。

由于统对任何内存区域的访问都不进行访问权限的检查,所以无论CPU处于合种模式下(Supervisor模式或是User模式),程序对该描述符描述的内存都可以顺利地进行读写操作

例3:Discriptor 中的domain=4,AP=11(这种情况下S bit ,A bit 被忽略)

由于domain=4,而DOMAIN ACCESS CONTROL REGISTER中field 4的值是01,系统会对该访问进行访问权限的检查。

由于AP=11,所以无论CPU处于合种模式下(Supervisor模式或是User模式),程序对该描述符描述的内存都可以顺利地进行读写操作

例4:

Discriptor 中的domain=4,AP=00, S bit="0",A bit="0"

由于domain=4,而DOMAIN ACCESS CONTROL REGISTER中field 4的值是01,系统会对该访问进行访问权限的检查。

由于AP=00,S bit="0",A bit="0",所以无论CPU处于合种模式下(Supervisor模式或是User模式),程序对该描述符描述的内存都只能进行读操作,否则引起permission fault.

通过以上4个例子我们得出两个结论:

1.对某个内存区域的访问是否需要进行权限检查是由该内存区域的描述符中的Domain域决定的。

2.某个内存区域的访问权限是由该内存区域的描述符中的AP位和协处理器CP15中Control Register1(控制寄存器1)中的S bit和R bit所决定的。

ARMMMU工作原 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)