关于单片机的计时器与中断系统

时间:11-23

来源:互联网

点击:

关于嵌入式,我就自己的XXX长话短说一下,说来话就长了,学过Java、Java

下面进入正题:

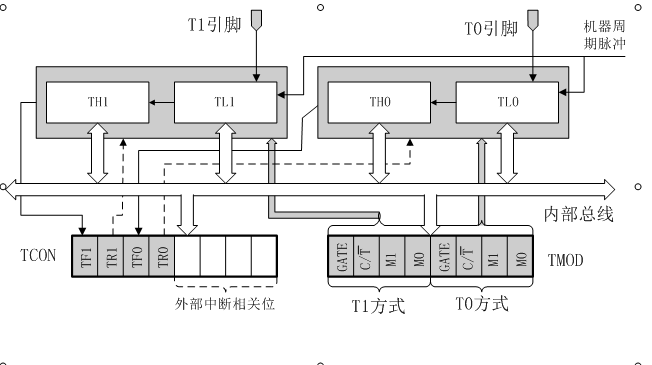

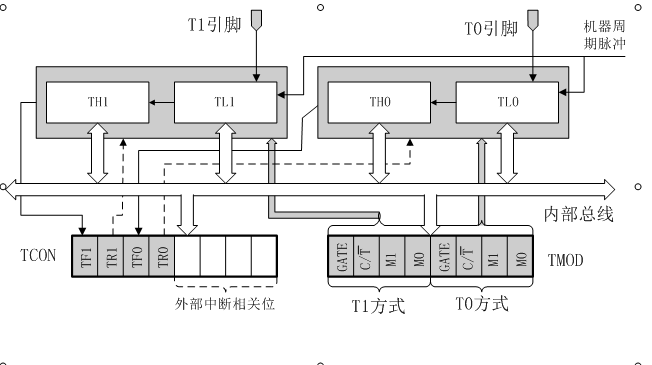

其中可以清楚的看到,TH0和TL0是两个8位寄存器,这两个寄存器组合成T0加1计数器,所以计数器为16位计数器。同理,TL1和TH1组合成了T1加1计数器。

再看TMOD寄存器,它是一个8位寄存器,名字叫做工作方式寄存器,显然它是控制工作方式的,看电路图上看它有两条灰色的线条延伸到T0和T1,即它可控制T0和T1的工作方式,也可以清楚的看到,其低四位控制T0的工作方式,高4位控制T1的工作方式。

那么什么叫做工作方式呢?工作方式就是指开或者关,芯片是工作在定时模式还是计数模式,和寄存器的使用情况。总体如下:

GATE是门控位,GATE=0时,TCON中TR0/TR1=1时可启动。

GATE=1时,TCON中TR0/TR1=1,且外部中断引脚为高电平时可启动。

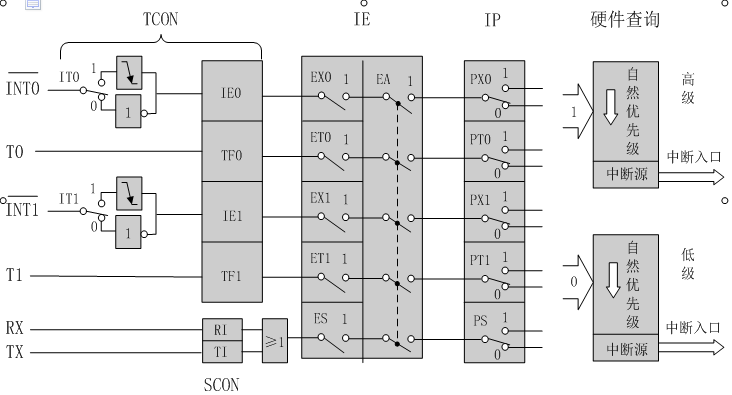

看这图估计都没心情,下面剖开来看:

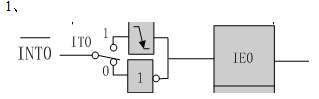

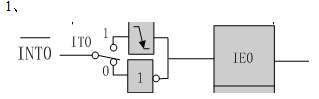

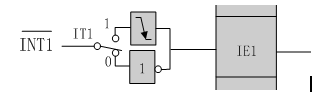

其他的先不看,先看这点图,这是一个中断源,其中IT0是选择中断的方式,IT0=1时为选择下降沿有效,IT0=0时为低电平有效(有一个非门)。当中断触发时就将IE0置1,此时,向CPU申请中断。那么,IT0和IE0是在什么地方呢?

还记得上面讲的TCON吗?现在把低四位也加进去:

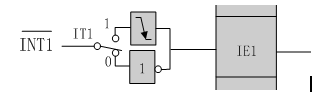

2、

参照1:INT0。

3、

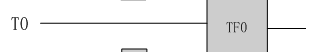

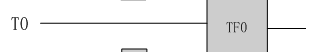

TF0中断,上面已经介绍。

4、

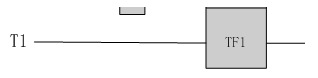

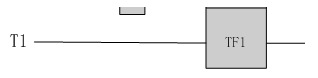

TF1中断,上面已经介绍。

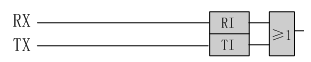

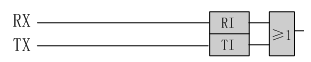

5、(RI或TI中断)

串行口中断请求标志,当串行口接收完一帧串行数据时,置位RI或当串行口发送完一帧串行数据时置位TI,向CPU申请中断。

IT0:外部中断0触发方式门控位。

·IT0=0为下降沿有效

·IT0=1为负边沿触发

IE0:外部中断0中断请求标志位。

IT1:外部中断1触发方式控制位(同IT0)。

IE1:外部中断1中断请求标志位。

TF0:T0溢出中断。

TF1:T1溢出中断。

RI:串行口接收中断标志位。当允许串行口接收数据时,每接收完一个串行帧,由硬件置位RI,同样,RI必须由软件清除。

TI:串行口发送中断标志位。当CPU将一个发送数据写入串行口发送缓冲器时,就启动了发送过程,每发送完一个串行帧,由硬件置位TI,CPU响应中断时,不能自动清除TI,TI必须由软件清除。

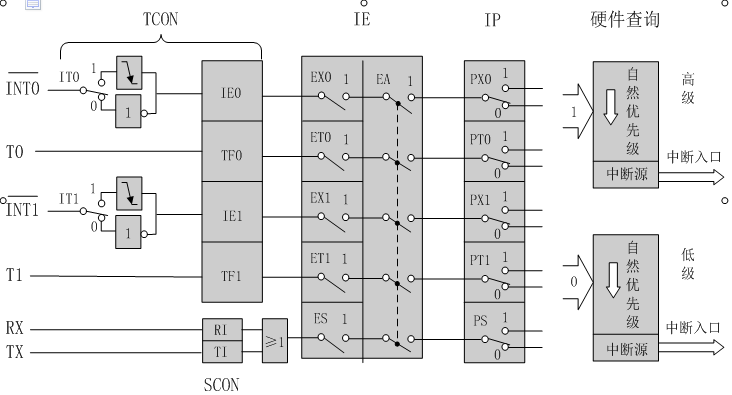

下面再看上图的下一部分:

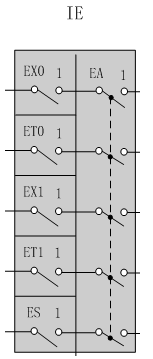

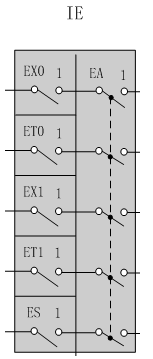

这部分叫做中断允许控制,当一个中断发生时,必须由中断允许控制来检测是否允许,如果允许则转入中断处理,否则不处理。

先看右边的EA,这个是总的中断允许控制位,CPU想要处理中断,必须开此中断允许。

再看左边:

其中各个中断允许控制如下:

·EX0:外部中断0允许位

·ET0:T0中断允许位

·EX1:外部中断1允许位

·ET1:T1中断允许位

·ES:串行口中断允许位

其中,这几个位都是由中断允许寄存器IE控制的,IE寄存器具体如下:

很明了,中断响应条件如下:

1、有中断请求

2、中断源中断允许位为1

3、CPU开中断(EA=1)

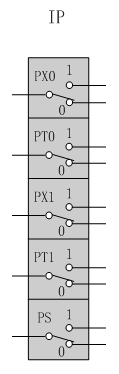

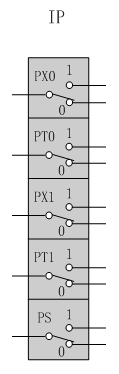

其中,8051有两个中断优先级,可以实现二级中断嵌套。每个中断源的中断优先级都是由中断优先级寄存器IP中的相应位的状态来规定的。

IP寄存器如下:

下面进入正题:

1、计时器

下面先看一个图:

其中可以清楚的看到,TH0和TL0是两个8位寄存器,这两个寄存器组合成T0加1计数器,所以计数器为16位计数器。同理,TL1和TH1组合成了T1加1计数器。

再看TMOD寄存器,它是一个8位寄存器,名字叫做工作方式寄存器,显然它是控制工作方式的,看电路图上看它有两条灰色的线条延伸到T0和T1,即它可控制T0和T1的工作方式,也可以清楚的看到,其低四位控制T0的工作方式,高4位控制T1的工作方式。

那么什么叫做工作方式呢?工作方式就是指开或者关,芯片是工作在定时模式还是计数模式,和寄存器的使用情况。总体如下:

GATE是门控位,GATE=0时,TCON中TR0/TR1=1时可启动。

GATE=1时,TCON中TR0/TR1=1,且外部中断引脚为高电平时可启动。

看这图估计都没心情,下面剖开来看:

其他的先不看,先看这点图,这是一个中断源,其中IT0是选择中断的方式,IT0=1时为选择下降沿有效,IT0=0时为低电平有效(有一个非门)。当中断触发时就将IE0置1,此时,向CPU申请中断。那么,IT0和IE0是在什么地方呢?

还记得上面讲的TCON吗?现在把低四位也加进去:

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

参照1:INT0。

3、

TF0中断,上面已经介绍。

4、

TF1中断,上面已经介绍。

5、(RI或TI中断)

串行口中断请求标志,当串行口接收完一帧串行数据时,置位RI或当串行口发送完一帧串行数据时置位TI,向CPU申请中断。

TCON中断

其中,TCON中的中断标志有如下几个:| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

·IT0=0为下降沿有效

·IT0=1为负边沿触发

IE0:外部中断0中断请求标志位。

IT1:外部中断1触发方式控制位(同IT0)。

IE1:外部中断1中断请求标志位。

TF0:T0溢出中断。

TF1:T1溢出中断。

SCON中断

SCON中的中断如下:| TI | RI |

TI:串行口发送中断标志位。当CPU将一个发送数据写入串行口发送缓冲器时,就启动了发送过程,每发送完一个串行帧,由硬件置位TI,CPU响应中断时,不能自动清除TI,TI必须由软件清除。

下面再看上图的下一部分:

这部分叫做中断允许控制,当一个中断发生时,必须由中断允许控制来检测是否允许,如果允许则转入中断处理,否则不处理。

先看右边的EA,这个是总的中断允许控制位,CPU想要处理中断,必须开此中断允许。

再看左边:

其中各个中断允许控制如下:

·EX0:外部中断0允许位

·ET0:T0中断允许位

·EX1:外部中断1允许位

·ET1:T1中断允许位

·ES:串行口中断允许位

其中,这几个位都是由中断允许寄存器IE控制的,IE寄存器具体如下:

| EA | ES | ET1 | EX1 | ET0 | EX0 |

很明了,中断响应条件如下:

1、有中断请求

2、中断源中断允许位为1

3、CPU开中断(EA=1)

其中,8051有两个中断优先级,可以实现二级中断嵌套。每个中断源的中断优先级都是由中断优先级寄存器IP中的相应位的状态来规定的。

IP寄存器如下:

| PT2 | PS | PT1 | PX1 | PT0 | PX0 |