ARM与不同位宽存储器的地址线错位接口

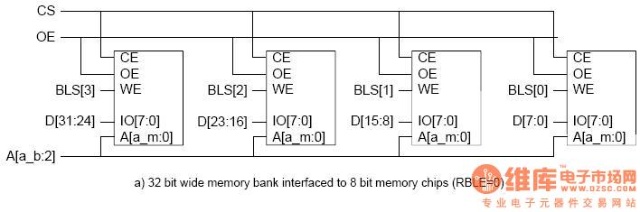

32位的FLASH,FLASH的A0要接ARM的A2,因为32位地址表示4个字节,每次要跳4个字节的话,那么就是从A2开始才变化,A1 A0不变化

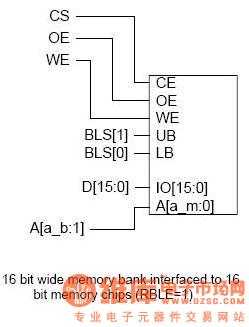

16位的FLASH,FLASH的A0要接ARM的A1,因为16位地址表示2个字节,每次要跳2个字节的话,那么就是从A1开始才变化,A0不变化

8位的FLASH,FLASH的A0要接ARM的A0,因为8位地址表示1个字节,每次要跳1个字节的话,那么就是从A0开始才变化。

这个地址对应于ARM发出的地址的A[21..1],即实际上是存储器需要的偶地址(偶地址是针对ARM发出的地址而言的)。

了,三星的如S3C2443\S3C2450\S3C6410等后续的也都是这样子了

BLS[1]、BLS[0]分别接到了存储器芯片的UB、LB脚。作为16位的存储器芯片,要取得16位宽度的字,无论是读访问还是写访问,UB和LB位都必须为低电平0。作为16位的ram,程序中不可避免的存在对它的写操作。程序能正常运行就说明对它的写操作是成功的。可以进一步推断在写访问期间,BLS[1] 、BLS[0]是低电平的。当存储器组为含有字节选择选择输入的16位或32位存储器组成的时候,RBLE位应该为1,在读访问期间EMC将BLS[3:0]拉低。在写访问周期EMC同样是将BLS[3:0]拉低。

这种操作也符合使用8位单片机时候的习惯,WR扮演了“写”的角色。

网友wag提出这样的问题,能否用ARM的WE引脚直接连接到存储器芯片的WE引脚。有这样的问题可能是源于以前的习惯,也可能是不清楚RBLE位为0时,写访问期间BLS[3:0]引脚的状态。

LPC2210/2220 User Manual 上面介绍了RBLE=0的时候的读写情况。EMC的WE信号没有被使用。在写周期,BLS[3:0]拉低,将数据送到要写入的地址。对于读周期,BLS[3:0]拉高。

网友sky421提到“我用的是2214,接一片8位的RAM,写的时候WE脚不会有变化,BLS0在变化”

我个人理解,如果RBLE=0,BLS引脚就取代了WR的功能,WR脚就不可以使用了。

有心的朋友可以用逻辑分析仪测一下,实际情况如何,验证一把。

总结,当RBLE=1,WR 有效,BLS充当字节选择,其随WR,OE的变化而变化,读、写操作时 BLS都是低电平,此时用于有字节选择的外部设备。

不是ARM9 S3C2440的,但是有相似之处!

存储器映射:

0-1G(0x0000,0000 - 0x3fff,ffff):片内Flash.

1-2G(0x4000,0000 - 0x7fff,ffff):片内RAM.

2-3.5G(0x8000,0000 - 0xbfff,ffff - 0xdfff,ffff):片外存储器。

3.5G - 3.75G(0xe000,0000 - 0xefff,ffff): VPB外设。

3.75G - 4G(0xf000,0000 - 0xffff,ffff): AHB外设。

虽然ARM7的寻址空间为4G,但是LPC2200系列只提供A0~A23总共16M的地址。片选信号CS0 - CS3是A24和A25的译码输出,将片外存储区0x8000,0000 - 0x83ff,ffff划分为bank0 - bank3,共16M*4=64M.这4个bank可以被分别配置为8/16/32位总线宽度。复位时,bank0的总线宽度由Boot1:0引脚决定, bank1为32位,bank2为16位,bank3为8位。

字节定位信号(BLS0 - BLS3)协调总线宽度和外存芯片数据线宽度。

当Memory由“字节宽度器件”(如62256)或者“未按照字节区分的多字节器件”组成时,应将RBLE设置为"0"。此时,读访问时EMC将BLS0~BLS3拉高。

当Memory由“含有字节选择输入的16位或32位器件”组成时,应将RBLE设置为"1"。此时,读访问时EMC将BLS0~BLS3拉低。

所以,当Memory由62256组成时,由于不需要“片内字节选择输入”,故令RBLE = 0,则BLS0~BLS3只会与nWR同步,可以代替nWR使用。

但是,当Memory由IS61LV25616AL组成时,由于该芯片有"nLB"和"nUB"控制低/高8位的输入,故令RBLE = 1,则BLS0~BLS3与nRD和nWR都会同步,此时,不可以使用BLS0~BLS3代替nWR信号。

地址数据总线:D0 - D31, A0 - A23, OE, WE, CS0 - CS3, BLS0 - BLS3

启动后由P2.7/P2.6控制引导方式,然后由程序设置MEMMAP决定中断向量的映射。

BCFG0 - BCFG3控制读写延时和总线宽度。注意复位后的默认值。

PINSEL2控制引脚功能。

Boot Block

LPC2114/2214的BootBlock被固化在最高的Flash块中,运行时被映射到0x7FFF,E000 - 0x7FFFF,FFFF的区域。而LPC2210没有片内Flash,但它有8K片内ROM存储了BootBlock,也被映射到0x7FFF,E000处。

ARM位宽存储器地址线错位接 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)