MSP430X5XX的时钟系统与低功耗模式

时间:11-25

来源:互联网

点击:

引言:全新改版,关于MSP430x5xx时钟系统与低功耗模式介绍。用到低功耗的时候,不得不仔细的看文档,做比较实验,真繁琐。

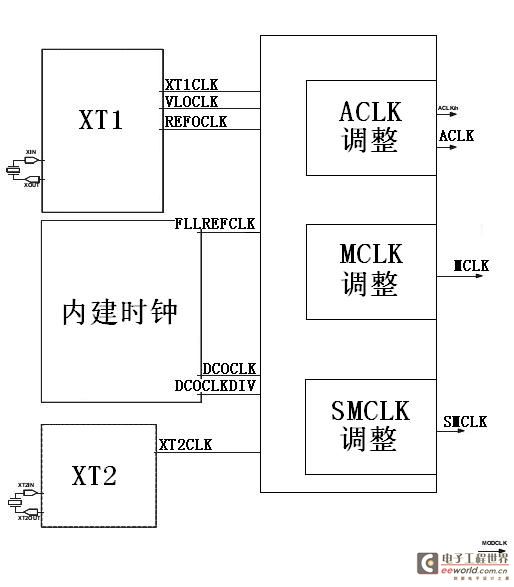

左边的模块——XT1、内建时钟(DCO)、XT2用来产生时钟源,也就是右边最终输出的时钟信号的基准信号。

而时钟调整模块负责将源时钟信号选通、分频输出成系统使用的三大时钟信号——MCLK,ACLK和SMCLK,分别是系统的主时钟(供CPU使用),辅助时钟(可给外设模块使用,也可以从管脚引出),子系统时钟(外设模块时钟,可从管教引出)。

2. 调整模块

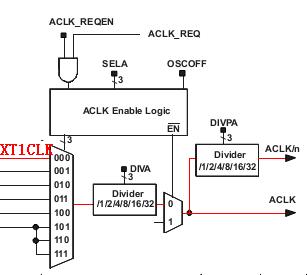

调整模块的主要工作分为两步:选通、分频。ACLK调整模块如下图所示

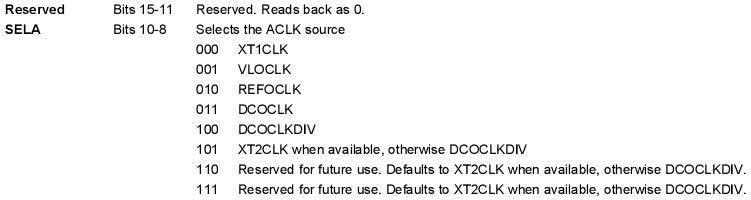

SELA具体的含义如下图所示:

3.REFO、VLO和DCO

有了上述的理解,再参照slau208e,我相信不难写出我们想要的代码。不过整个UCS中最有特色的部分还没有介绍,那就是REFO、VLO和DCO。

REFO是内建的参考时钟,它很稳定,可以作为FLL的时钟基准(FLL是什么待会再说)。MSP430F5418上的REFOCLK是32.768kHz的。

VLO是一个内建的低频时钟。在5418上,它的频率是8.6kHz。

DCO是Digitally-Controlled Oscillator,数控晶振。它可以产生频率很高的时钟。通过配置,它可以产生百兆以上的时钟信号。在5418上,电压等级1的时候,不用XT2,有FLL(这个FLL到底是什么呢?),我调出的最高频率是26MHz。

吊了这么半天胃口,来说一下这个FLL是什么东西。

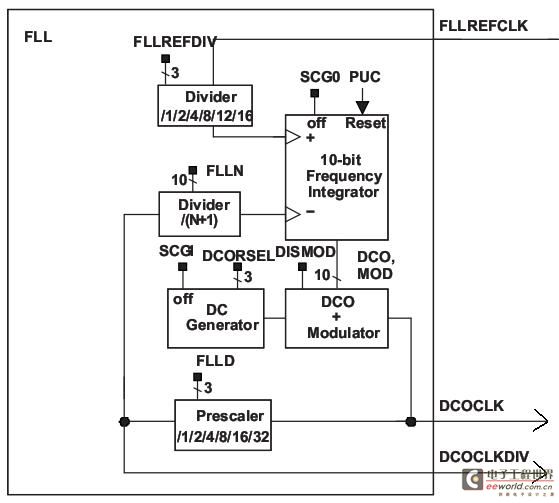

FLL是Frequency Locked Loop,锁频环。先来个特写

4.频率范围和电压等级

MSP430把内核的工作频率划分为若干范围,比如543x和541x的工作频率就被分为了8个范围。每个范围又被DCO这个参数分为了32个小段,每个小段又被MOD分为32个小小段(待验证)。所以可以把DCO看作是粗调旋钮,MOD是微调旋钮。另外,需要注意的是,这个频率范围是指DCO的频率范围,当DCO被禁用的时候,这个范围就没意义了。

喜欢超频的同学都知道,核心电压和工作频率之间有着密切的关系。430单片机也是如此,它有4个电压等级,涵盖了从1.2V到2V广阔的核心电压范围。

一般来说,核心电压越高,频率范围越大,功耗越大;核心电压越低,频率范围越小,功耗越小。

当电压等级为1的时候(默认电压等级),5418的各个频率范围的可用上下限如下表所示:

430系列单片机中有各种时钟信号,第一次接触免不了一头雾水。而且如果想发挥430低功耗的优势,就不得不对它的时钟系统(Unified Clock System)有所了解。

1. 时钟模块总览

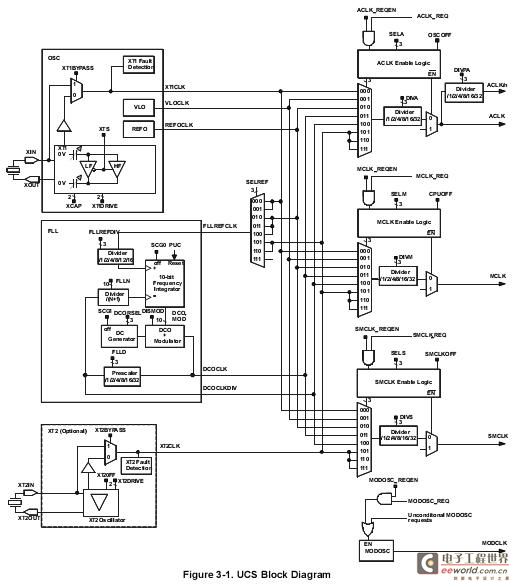

这是MSP430X5XX的时钟系统框图。乍一看很复杂,不过简化之后就清楚多了

左边的模块——XT1、内建时钟(DCO)、XT2用来产生时钟源,也就是右边最终输出的时钟信号的基准信号。

而时钟调整模块负责将源时钟信号选通、分频输出成系统使用的三大时钟信号——MCLK,ACLK和SMCLK,分别是系统的主时钟(供CPU使用),辅助时钟(可给外设模块使用,也可以从管脚引出),子系统时钟(外设模块时钟,可从管教引出)。

2. 调整模块

调整模块的主要工作分为两步:选通、分频。ACLK调整模块如下图所示

左端进线是源时钟信号。红色标出来的是XT1CLK信号。由图易知,XT1CLK要变成ACLK信号,需要经过两次选通,一次分频,也就是我红色标出来的路径。第一个选通器可通过设置SELA来控制,分频器可以通过设置divA来控制,正常工作的时候,最后一个选通器总是打开的,这里不讨论。换言之,要想设置ACLK,我们只需要配置SELA和divA。例如,如果我们希望ACLK是XT1CLK的2分频的话,需要设置SELA={0},divA={1}。再给一个来自TI的例子

UCSCTL4 |= SELA_2;这句话将ACLK的源设置为REFO。// Set ACLK = REFO

SELA具体的含义如下图所示:

3.REFO、VLO和DCO

有了上述的理解,再参照slau208e,我相信不难写出我们想要的代码。不过整个UCS中最有特色的部分还没有介绍,那就是REFO、VLO和DCO。

REFO是内建的参考时钟,它很稳定,可以作为FLL的时钟基准(FLL是什么待会再说)。MSP430F5418上的REFOCLK是32.768kHz的。

VLO是一个内建的低频时钟。在5418上,它的频率是8.6kHz。

DCO是Digitally-Controlled Oscillator,数控晶振。它可以产生频率很高的时钟。通过配置,它可以产生百兆以上的时钟信号。在5418上,电压等级1的时候,不用XT2,有FLL(这个FLL到底是什么呢?),我调出的最高频率是26MHz。

吊了这么半天胃口,来说一下这个FLL是什么东西。

FLL是Frequency Locked Loop,锁频环。先来个特写

FLLD,FLLN,FLLREFdiv,FLLREFCLK计算公式如下:

fDCOCLK = D × (N + 1) × (fFLLREFCLK ÷ n)其中

fDCOCLKdiv = (N + 1) × (fFLLREFCLK ÷ n)

D=1,2,4,8,16,32(对应FLLD=0,1,2,3,4,5)比如,我们想设置DCO输出1MHz的时钟信号,可以设置这样一组值:

N=FLLN

n=1,2,4,8,12,16(对应FLLREFdiv=0,1,2,3,4,5)

fFLLREFCLK为REFOCLK,XT1或XT2的实际频率。

FLLD=1,对应D=2;FLLN=60;FLLREFdiv=2,对应n=4;fFLLREFCLK=fREFOCLK=32.768kHz所以

fDCOCLK=2×(60+1)×(32.768/4)=999.424kHz,fDCOCLKdiv=fDCOCLK/2=499.712kHz实际测试fDCOCLK=1.006MHz。

4.频率范围和电压等级

MSP430把内核的工作频率划分为若干范围,比如543x和541x的工作频率就被分为了8个范围。每个范围又被DCO这个参数分为了32个小段,每个小段又被MOD分为32个小小段(待验证)。所以可以把DCO看作是粗调旋钮,MOD是微调旋钮。另外,需要注意的是,这个频率范围是指DCO的频率范围,当DCO被禁用的时候,这个范围就没意义了。

喜欢超频的同学都知道,核心电压和工作频率之间有着密切的关系。430单片机也是如此,它有4个电压等级,涵盖了从1.2V到2V广阔的核心电压范围。

一般来说,核心电压越高,频率范围越大,功耗越大;核心电压越低,频率范围越小,功耗越小。

当电压等级为1的时候(默认电压等级),5418的各个频率范围的可用上下限如下表所示:

5418各频率范围上下限详表从这个表中可以看出,除了前边谈到的几个参数,还有大量的其他寄存器参数。具体的含义可以从参考文献中查知。如果觉得翻看pdf太

MSP430X5XX时钟系统低功耗模 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)