STM32F103 FSMC同步模式学习笔记2

时间:11-26

来源:互联网

点击:

苦逼了。。看了将近一个礼拜的STM32F103 FSMC 片选NOR的异步模式。。。。可能对项目提升不大。。。现在看同步突发模式。。我也不知道怎么翻译。。。嵌入式学得不太久。。不说了 一会看手册啊。。

----------------------------------我是无耻的分割线-----------------------------------------------

首先对于NOR异步模式总结一下:

1.硬件线路一定要对

2.需要知道可以用一根地址线(Ax)或者一些地址线选择RS或者其他的东西,很有用。

3.我用的是不复用模式144脚,如果是复用模式可能地址线会更乱一些。

4.一定要先初始化RCC,GPIO在初始化FSMC。。要不可能会有问题,经验之谈。。

5.21IC上有好多FSMC的帖子。。很有用。。

6.要去官网下appliction note和芯片手册。。最权威

之后对于一些要重复记忆的话:

FSMC所有输出信号都是上升沿有效。

最后给出我用示波器测试出来数据:

ADDSET = 0

ADDSET = 0

ADDSET = 15 DATASET = 255 实际数据传输率: 260KHz (接近最慢)

异步模式NE也就是信号有点奇怪,我认为他是片选信号,但是为什么会根据transaction拉低,transaction结束后又拉高,维持一固定一小段时间??(有待继续看手册)

经过异步模式的测量与验证,按照时序计算,一次transaction(NE从低到高的过程),时间计算和手册是一样的:

我用的是扩展模式B: Tclc(write) =

其中ADDSET最小为0,而DATASET最小为1.

手册上没有的知识,经过一下午的测量,得出NE信号的恢复时间,即transaction结束后,NE拉高,再拉地的时间大致为6个HCLK。(如果同步模式和你的分频有关,为6个CLK)

-------------------------------------------------------------------------------------------------

下面是同步模式:

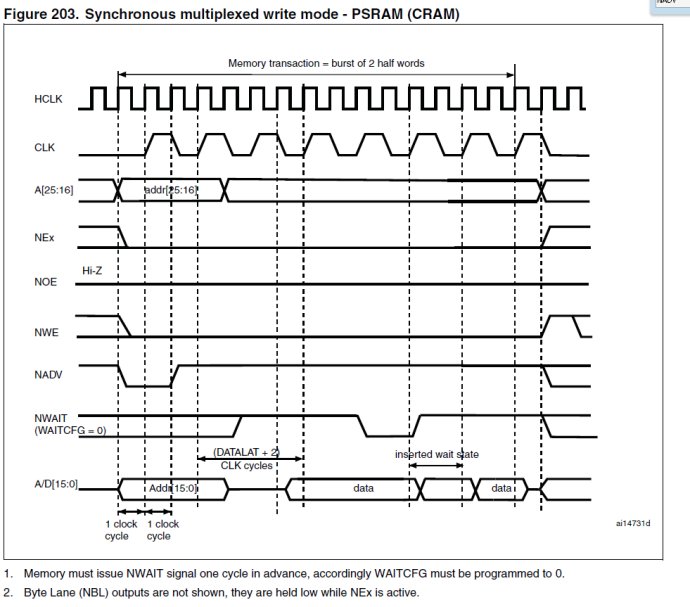

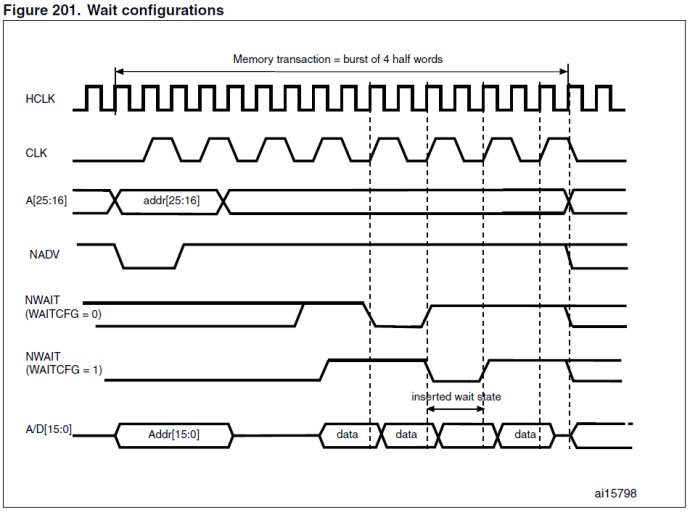

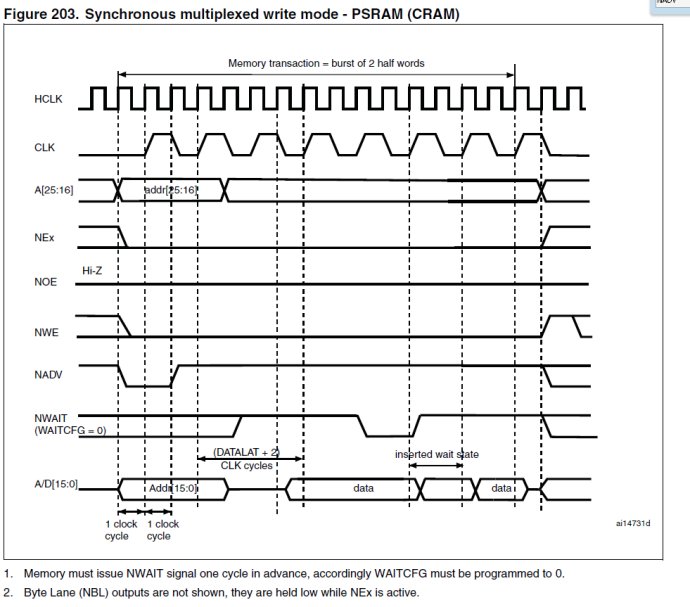

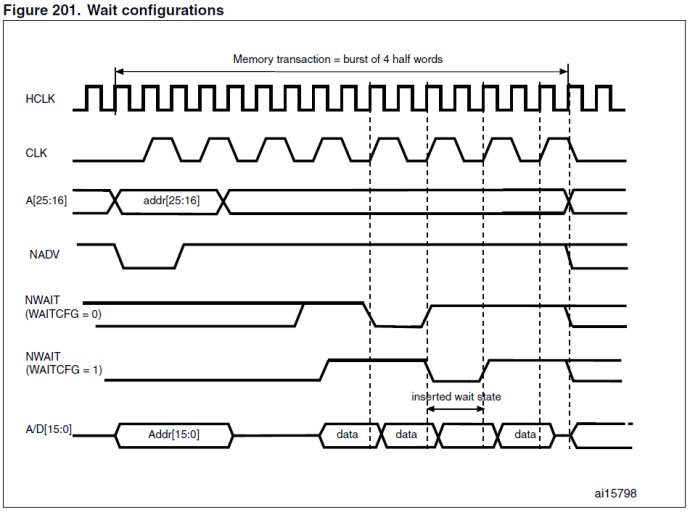

为了保证memory clock(CLK)在NADV低电平的中间上升,FSMC会在一个HCLK周期后操作CLK(在NADV前)。

Data latency:就是在采样前等待的时间周期,但是不包括NADV为低时的时间,可以从图1看出。

注意的是:一些NOR FLASH包括NADV为低时的周期,所以有下面的情况

NOR Flash latency = DATLAT + 2

NOR Flash latency = DATLAT + 3

同步模式代码我贴出来吧:

void LED_FSMCConfigMy(void)

{

}

另外,我用红色高亮的代码是我遇到问题后的解决方案,就是不论你怎么设置分频和时延,都是预期的结果。

http://bbs.21ic.com/viewthread.php?tid=375165&highlight=

原因很简单:

因为

----------------------------------我是无耻的分割线-----------------------------------------------

首先对于NOR异步模式总结一下:

1.硬件线路一定要对

2.需要知道可以用一根地址线(Ax)或者一些地址线选择RS或者其他的东西,很有用。

3.我用的是不复用模式144脚,如果是复用模式可能地址线会更乱一些。

4.一定要先初始化RCC,GPIO在初始化FSMC。。要不可能会有问题,经验之谈。。

5.21IC上有好多FSMC的帖子。。很有用。。

6.要去官网下appliction note和芯片手册。。最权威

之后对于一些要重复记忆的话:

FSMC所有输出信号都是上升沿有效。

最后给出我用示波器测试出来数据:

ADDSET = 0

ADDSET = 0

ADDSET = 15 DATASET = 255 实际数据传输率: 260KHz (接近最慢)

异步模式NE也就是信号有点奇怪,我认为他是片选信号,但是为什么会根据transaction拉低,transaction结束后又拉高,维持一固定一小段时间??(有待继续看手册)

经过异步模式的测量与验证,按照时序计算,一次transaction(NE从低到高的过程),时间计算和手册是一样的:

我用的是扩展模式B: Tclc(write) =

其中ADDSET最小为0,而DATASET最小为1.

手册上没有的知识,经过一下午的测量,得出NE信号的恢复时间,即transaction结束后,NE拉高,再拉地的时间大致为6个HCLK。(如果同步模式和你的分频有关,为6个CLK)

-------------------------------------------------------------------------------------------------

下面是同步模式:

为了保证memory clock(CLK)在NADV低电平的中间上升,FSMC会在一个HCLK周期后操作CLK(在NADV前)。

Data latency:就是在采样前等待的时间周期,但是不包括NADV为低时的时间,可以从图1看出。

注意的是:一些NOR FLASH包括NADV为低时的周期,所以有下面的情况

NOR Flash latency = DATLAT + 2

NOR Flash latency = DATLAT + 3

同步模式代码我贴出来吧:

void LED_FSMCConfigMy(void)

{

}

另外,我用红色高亮的代码是我遇到问题后的解决方案,就是不论你怎么设置分频和时延,都是预期的结果。

http://bbs.21ic.com/viewthread.php?tid=375165&highlight=

原因很简单:

因为

STM32F103FSMC同步模 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)