基于UHF RFID标签芯片PIE解码电路的实现方案

Pivot=RTcal/2,即1.25 Tari<=Pivot<=1.5 Tari

本文提出对上述判决标准进行一系列等效变换。将新的判决标准称为New Pivot,简称为NP。

NP=(Tari+RTcal)/3

3.5 Tari/3<=NP<=4.0 Tari/3即1.16 Tari<=NP<=1.33 Tari

显然仅对数据"0"和数据"1"而言,如果符号长度小于NP,则可以判决为数据"0",如果符号长度大于NP,则可以判决为数据"1"。使用新的等效判决条件,带来两个好处,首先NP与数据"1"长度上有了明显的区隔,避免旧的pivot在等于1.5 Tari时可能造成的混淆,新的判决条件对数据"0"和数据"1"均保留一定的安全距离,使得我们可以简化比较逻辑;其次,旧的判决条件从1.25至1.5有16.7%的变动范围,而新的判决条件从1.16至1.33有12.7%的变动范围,变动范围减少了24%,这显著地缩小了采样时亚稳态造成的误差范围。

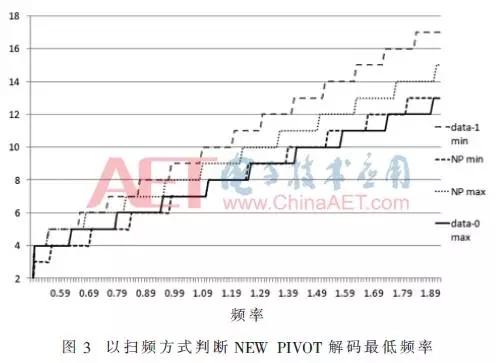

假设在最严格的条件(下行速率为160 kb/s,数据"1"为1.5 Tari,考虑亚稳态影响采样得到的数据"1"最小值、数据"0"最大值、NP最大值、NP最小值,阅读器正负百分之一的误差等)下,通过扫频来区分最大的Data-0与最小的Data-1,得到系统时钟最低频率为1 MHz左右,比pivot判决方法降低了37%。

如图3所示,在此频率以上时,NP的最大值小于数据"1"的最小值,而NP的最小值则不小于数据"0"的最大值,可以清楚地分离开逻辑符号"0"和"1"的长度。

2 解码电路设计方案

2.1 解码电路结构

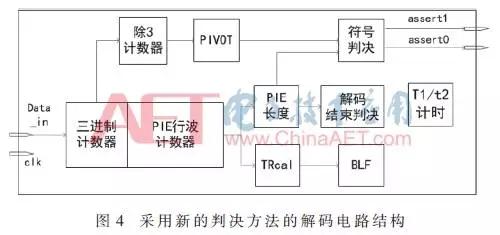

采用新的等效判决方法的解码电路结构如图4所示。主要包括混合式行波计数电路(由三进制计数、行波计数等组成)、符号判决电路、BLF计算电路及t1、t2时间计时器等模块组成。

2.2 解码判决逻辑

首先构造用于比较和判决的标准时间长度值,用系统时钟对TARI和RTcal进行计数,得到以时钟周期长度为单位的计数值,该计数值除3后,四舍五入的结果记为NP。

其次,对后续符号(一段高电平跟一段低电平)的长度进行计数,如果RTcal后面的符号长度大于2倍的NP,则判决为TRcal,如果符号长度大于NP,则判决为逻辑"1",如果符号长度小于等于NP,则判决为逻辑"0"。最后,如果高电平长度大于4倍的NP,则判断PIE编码结束。

为了与上行链路的频率保持一致,并考虑到时钟生成电路的精度偏差,我们选择1.28 MHz(精度7%)作为系统时钟频率。

2.3 解码计数电路

解码计数器包括CNTA与CNTB两部分,其中CNTA是三进制计数器,而CNTB 是行波计数器。

在计算NP时,如果使用除法器来实现除3,面积将显著增大,处理周期增加,功耗也会升高,因此我们使用三进制计数器(记为CNTA)来达到除3的效果。CNTA以0、1、2、0、1、2的规律进行计数,每当计数到2的时候,NP加1。在RTcal结束的时候,得到NP的计数值。该计数法与除3并四舍五入的结果完全一致,不会损失精度。

其次,在RTcal之后,以系统时钟频率对符号的高电平、低电平进行计数,由于系统时钟频率较快,计数器功耗比较大,因此我们组合使用CNTA与行波计数器CNTB取代了普通的同步计数器。

CNTB计数器的最低位使用系统时钟作为同步时钟端,其输出的Q端,反向后接到下一比特的时钟端,作为异步时钟端,以此类推。使用行波计数器,后一级的工作频率比前一位慢一倍,因此能够有效地降低功耗。

这样,混合计数器在Tari+RTcal阶段用作三进制计数,输出结果为NP;在RTcal阶段之后用作符号长度计数器,输出结果为当前符号计数值。

3 仿真结果

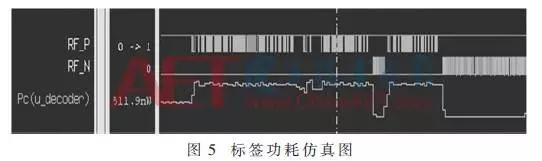

本文基于上述电路结构,在TSMC 0.18 μs CMOS工艺下进行电路实现。分别对采用1.92 MHz工作时钟的传统解码电路和使用1.28 MHz工作时钟的新型PIE解码电路进行了功耗仿真。

通信参数配置为:阅读器下行链路通信速率为160 KHz;Tari=6.25 μs;Data1=1.5 Tari=9.375 μs。在通信激励完全相同的情况下,当解码电路的工作时钟频率从1.92 MHz降低至1.28 MHz时,decoder电路的功耗由原先的0.8 μW变化为0.5 μW,降低约38%。图5为标签与阅读器通信交互过程的功耗仿真图分布。

4 结论

基于ISO 18000-6 Type C标准,实现了PIE解码电路的设计。我们通过等效的PIE符号判决条件找到了适合标签芯片的较低系统时钟频率1.28 MHz,并专门设计了三进制计数代替除法器等电路,配合实施新的解码方案。在TSMC 0.18 μm CMOS工艺下完成了ASIC芯片设计,仿真结果符合协议要求。

- UHF无源标签的设计与选择 (09-04)

- 一种 UHF 带通滤波器的设计 (10-24)

- 采用射频能量获取技术的UHF传感标签(04-29)

- 无源RFID标签芯片灵敏度测试方法研究(06-24)

- 汽车门禁射频接收器阻抗匹配介绍(08-25)

- 快速运动UHF RFID标签群的防冲突分析(10-10)