单片机访问IIC总线技术

1.

2.

3.

4.

5.

连接到相同总线的IC数量只受到总线的最大负载电容400pF的限制,因为挂接的设备越多,在总线上产生的负载电容就越大,会严重影响数据的传输波形,导致总线无法正常工作。

6.

IIC典型应用:

1.

2.

IIC总线规范:

在用到微控制器的系统中,需要一些规范来协调不同设备间的通信。

IIC总线的概念:

IIC总线支持任何IC生产工艺(NMOS, CMOS. 双极性)。

两线:

SDA-串行数据

SCL-串行时钟

每个器件都有一个唯一的地址识别(微控制器,LCD驱动器,存储器或是键盘接口),而且都可以作为一个发送器或接收器 由器件的功能决定 很明显 LCD驱动器只是一个接收器 而存储器则既可以接收又可以发送数据 除了发送器和接收器外 器件在执行数据传输时也可以被看作是主机或从机(见表 1)主机是初始化总线的数据传输并产生允许传输的时钟信号的器件 此时 任何被寻址的器件都被认为是从机

表一:

| 描述 | |

| 发送数据到总线的器件 | |

| 从总线接受数据的器件 | |

| 初始化发送、产生时钟信号和终止发送的器件 | |

| 被主机寻址的器件 | |

| 同时有多于一个主机尝试控制总线,但不破坏报文 | |

| 是一个在多个主机同时尝试控制总线,但只允许其中一个控制总线并使报文不被破坏的过程 | |

| 两个或多个器件共用一个同步时钟信号的过程 |

主机、从机;接收机,发送机:

关系都是相对的并且只在数据传输的时候才会存在:

1)假设微控制器A(主)要给B(从)发送数据

1. A寻址B

2. A发送数据到B; A - 发送器

3. A终止发送

2)假设A(主)想从B(从)接受信息

1. A寻址B

2. A从B接受数据;A - 接收器 B - 发送器

3. A终止接收

总线仲裁过程:

多个主机同时尝试发送信息到总线,其他主机都产生“0”的情况下,首先产生“1”的主机讲丢失仲裁。

仲裁时的时钟信号是用线与到SCL线的主机产生的时钟的同步结合。

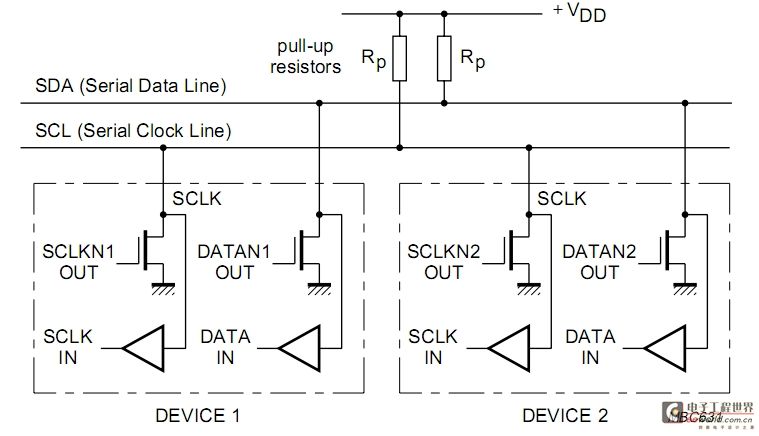

IIC总线接口电路:电路如下图

图中可以看出据诶大总线上的设备都是漏极(或集电极)开路,即OC门,只有OC们啊次可以实现总线上的线与。

数据的有效性:

SDA线上的数据必须在时钟的高电平周期保持稳定。数据线上的数据只能在SCL为低电平是才能改变。时序波

形

如下图:

start,stop

数据传送的起始和停止:

IIC总线中数据的起始和结束,与数据的位传输有所不同,

起始位:在SCL为高电平时,SDA从高电平向低电平切换

结束位:在SCL为高电平时,SDA从低电平向高电平切换

起始和结束位是由主机产生,总线在起始位开始之后被认为是处于忙状态,在出现结束位之后的某段时间后总线被确认为闲状态。

在起始条件产生后,停止条件产生前出现的起始条件和第一个起始条件在功能上是一样的。表示为(S)。

如果没有硬件检测总线起始和结束的设备想监视IIC总线(如微处理器),那么在每个周期至少采样两次SDA总线来确认有没有电平发生变化。

数据的传输:

字节格式传输:

SDA线上传输的数据必须是8位的,但每次可以传输多个字节。每个字节后面必须跟一个响应位。

总线上每个字节首先传送的是最高位(MSB)。

如果从机在接受数据前要完成一些工作(如中断服务程序)才能接受或发送数据,那么从机可以使时钟线SCL保

持低电平迫使主机进入等待状态。当从机准备好后接收下一个数据字节并释放时钟线后,数据传输继续。 在传

输数据时使用同样的方法也不会影响数据的传输。

响应位:

数据传输必须带响应。相关的响应脉冲由主机产生,在响应的时钟脉冲期间,发送器释放SDA线(此时为高电平)响应的时钟脉冲期间,接收器必须将SDA线拉低,并保持。(CBUS除外)

如果从机不能响应从机地址(在执行别的程序),从机必须使数据线保持高电平。主机会产生一个停止条件终止

传输或者产生重复起始条件开始新的传输。

如果从机接收器响应

单片机IIC总线技 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)