S5PV210(TQ210)学习笔记——内存配置(DDR2)

一 接线原理

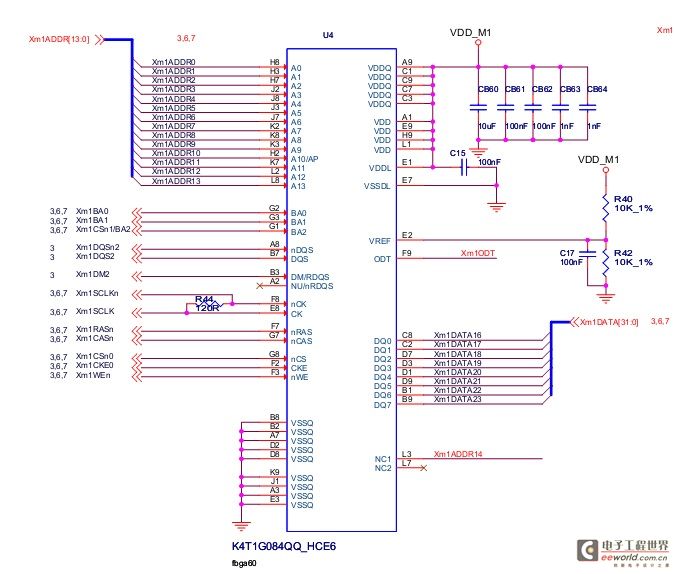

我的开发板是TQ210,开发板上有8片128M*8bits的内存芯片,从原理图上可以看到,其中4片并联接在DMC0上,另外四片并联在DMC1上,这里我只贴出一个链接方式,因为8片都是一样的,只是前四片跟后四片挂载的位置不同。

我们可以注意到,TQ210是将四片K4T1G084QQ的地址线并联,将数据线串联,这样正好是32位数据。另外,我们还可以看到K4T1G084QQ只接了14根地址线,这是因为K4T1G084QQ有14根行地址,10根列地址,这14根线是复用的。但是K4T1G084QQ有8个bank,而DMC只有两根bank线,为此,S5PV210给出了以下几个解决方案:

根据注释3,我们可以看到当S5PV210挂载8bank内存时CS1复用为BANK2,这中状态下S5PV210相当于只有一根片选引脚CS0,这样就可以理解了,我们从这里也可以知道配置num_chip参数时可以设置为1(经测试设置为2也可以,不过MEMCONFIG1的配置没有意思,因为8bank时只有CS0而没有CS1)。对于8banks且15根行地址的内存芯片也有一套解决方案,所以,一定要注意下面的注释,我当时配置时阅读手册就不够仔细,没有看下面的注释,结果卡了我一上午,没有弄明白内存芯片的接线原理,甚至认为开发板接线接错了。

二 地址映射

S5PV210的DMC跟6410和2440的DMC有个重要区别,S5PV210可以控制内存地址映射,DMC0的地址空间为0x2000,0000~0x3fff,ffff,DMC1的地址空间为0x4000,0000~0x7fff,ffff,DMC可以通过配置寄存器来使内存芯片映射到其内存段内的适当位置。这个配置在MEMCONFIG寄存器中,这个地址映射让我纠结了很长一段时间,最后还是查资料看明白的。

如果设置chip_base为0x20:

(1)我们挂载的内存为128M,那么这个chip_mask应该设置为0xF8

(2)我们挂载256M内存时,chip_mask应该设置为0xF0

(3)我们挂载512M时,chip_mask应该设置为0xE0

(4)我们挂载1GB内存时,chip_mask就应该设置为0xC0。

以DMC0为例,当DMC0接收到来自AXI的0x2000,0000~0x3fff,ffff内的地址时,会作如下处理:

(1)将AXI地址的高8位与chip_mask相与得到结果,记为X。

(2)将X分别与MEMCONFIG0和MEMCONFIG1的chip_base相比较,如果相等,则打开相应的片选。

假如挂载的内存为128M,且CS0和CS1上分别挂了一片,那么128M=128*1024*1024=0x8000000,则128M内存的偏移范围应该是0x0000,0000~0x07ff,ffff,高位剩余5位,那么,我们把MEMCONFIG0的chip_base设置为0x20,chip_mask设置为0xF8,为了保持内存连续,则需要将MEMCONFIG1的chip_base设置为0x28,chip_mask设置为0xF8,当AXI发来的地址为0x23xx,xxxx时,0x23&0xF8得到0x20,所以,会打开片选CS0,当AXI发来的地址为0x28xx,xxxx时,0x28&0xF8得到0x28,所以,会打开片选CS1,依此类推。

特别的,当载在的内存芯片为8bank(8bank内存芯片一般为14/15行地址,10列地址,即容量一般为512M或者1G)时,由于CS1为bank2引脚,为了保持CS0时钟处于片选状态,对于512M内存来讲需要将chip_mask设置为0xE0,这是因为512M=512*1024*1024=0x2000,0000,也就是说,512M内存的偏移应该为0x0000,0000~0x1fff,ffff,所以高位剩余3位,即0xE0,当然了,如果内存为1G=1024*1024*1024=0x4000,0000,即偏移为0x0000,0000~0x3fff,ffff,高位剩余2为,故设置chip_mask为0xC0。这样,就会计算偏移这两个值了。

三 配置流程

内存芯片的配置比较复杂,好在芯片手册上给出了常用内存类型的初始化序列,TQ210的内存是DDR2的,可以按照如下顺序进行初始化:

- 1.Toprovidestablepowerforcontrollerandmemorydevice,thecontrollermustassertandholdCKEtoalogiclowlevel.Thenapplystableclock.Note:XDDR2SELshouldbeHighleveltoholdCKEtolow.

- 2.SetthePhyControl0.ctrl_start_pointandPhyControl0.ctrl_incbit-fieldstocorrectvalueaccordingtoclockfrequency.SetthePhyControl0.ctrl_dll_onbit-fieldto‘1’toturnonthePHYDLL.

- 3.DQSCleaning:SetthePhyControl1.ctrl_shiftcandPhyControl1.ctrl_offsetcbit-fieldstocorrectvalueaccordingtoclockfrequencyandmemorytACpar

S5PV210内存配置DD 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)