[ARM笔记]存储控制器及其访问外设的原理

1. S3C2410/S3C2440地地址空间

S3C2410/S3C2440对外引出的27根地址线ADDR0~ADDR26的访问范围只有128MB,那么是如何达到1GB的空间的呢?CPU对外还引出了8根片选信号nGCS0~nGCS7,对应于BANK0~BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平用来选中外接的设备。这样,每个nGCSx对应128MB的地址空间,8个nGCSx信号总共就对应了1GB的地址空间。这8个BANK的地址空间如:http://weimenlove.blog.163.com/blog/static/17775473201101013847857/

S3C2410/S3C2440作为32位的CPU,可以使用的地址范围理论上可达到4GB。除去上述用于连接外设的1GB的地址空间外,还有一部分是CPU内部寄存器的地址,剩下的地址空间没有使用。注意:这里的地址指的是物理地址。

2. 存储控制器与外设的关系

所以要确定一个器件的地址,首先看它位于哪个Bank区,再看它连在Addr[26:0]地址线所确定的地址,将该区的起始值和它的地址线地址相加即得该器件的地址。

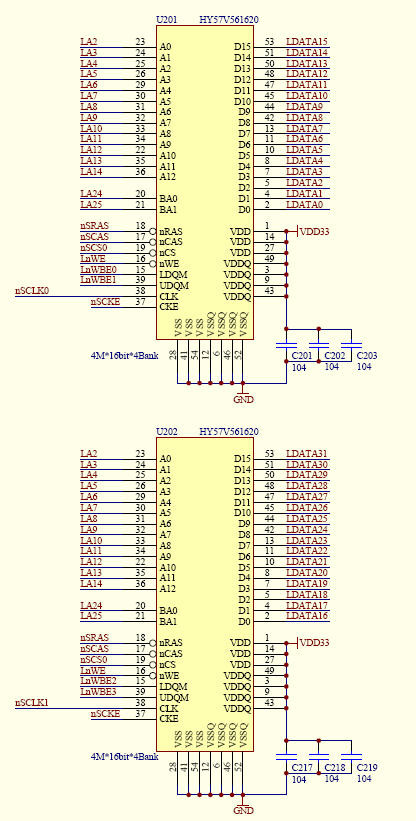

BANK0~BANK5的连接方式类似,BANK6连接SDRAM时复杂一点,CPU提供了一组用于SDRAM的信号。

1) SDRAM时钟有效信号SCLK;

2) SDRAM时钟信号SCLK0/SCLK1;

3) 数据掩码信号DQM0/DQM1/DQM2/DQM3;

4) SDRAM片选信号nSCS0(它与nGCS6是同一引脚的两个功能);

5) SDRAM行地址选通脉冲信号nSRAS;

6) SDRAM列地址选通脉冲信号nSCAS;

7) 写允许信号nWE(它不是专用于SDRAM)。

SDRAM的内部是一个存储阵列,阵列就如同表格一样,将数据“填”进去。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的单元格,这就是SDRAM寻址的基本原理。这个单元格被称为存储单元,这个表格(存储阵列)就是逻辑Bank(Logic Bank,下文简称L-Bank),SDRAM一般含有4个L-Bank。

可以想象,对SDRAM的访问可以分为如下4个步骤:

1)CPU发出的片选信号nSCS0有效,它选中SDRAM芯片。

2)SDRAM中有4个L-Bank,需要两根地址信号来选中其中一个,如图中所示的是用ADD24、ADD25作为L-Bank的片选信号。

3)对被选中的芯片进行统一的行/列(存储单元)寻址。

根据SDRAM芯片的列地址线数目设置CPU的相关寄存器后,CPU就会从32位的地址中自动分出L-Bank选择信号、行址址信号、列地址信号,然后先后发出行地址信号、列地址信号。L-Bank选择信号在发出行地址信号的同时发出,并维持到列地址信号结束。

在图中,行地址、列地址共用地址线ADD2~ADD14(BANK6的位宽为32,ADDR0/1没有使用),使用nSRAS、nSCAS两个信号来区分它们。如上图中,使用两根地址线Addr24、Addr25作为L-Bank的选择信号;HY57V561620使用13根行地址,9根列地址,所以当nSRAS信号有效时,ADDR2~ADDR14上发出的是行地址信号,它对应32位地址空间的bit[23:11];当nSCAS信号有效时,ADDR2~ADDR10上发出的是列地址信号,它对应32位地址空间的bit[10:2];由于Bank6以32位的宽度外接SDRAM,ADDR0、ADDR1恒为0,不参与译码。

又因为Bank6的起始地址为0x3000_0000,所以SDRAM的访问地址为0x3000_0000~0x33ff_ffff,共64MB(2片*(4*Bank*2^22)*16bit)。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)