PCI总线与接口技术

1、PCI总线的发展历史

1990年,起源于Intel架构开发实验室,全称是Peripheral Component Interconnect,首先在服务器中使用,代替了原来的MCA以及EISA,EISA直到2000年才宣告退出历史舞台。直到1994年,才开始在PC上广泛使用,代替了原来的VESA。在1995年的中期,苹果电脑也开始使用PCI总线电气规范。后来PCI也增加了许多新的功能,比如66MHz,3.3V标准,以及133MHz的PCI-X。2004年,出现了PCI-Express,原来的PCI总线电气规范被称为了传统PCI(Conventional PCI)。

2、PCI总线地址空间

独立的内存以及IO接口,由软件分配。而另外一个地址空间-PCI配置空间(PCI Configuration Space),使用独立的地址,允许软件决定每一个连入的设备需要多少内存以及IO地址空间。通过设备配置空间寄存器的设置,每一个设备至多可以申请6个内存以及IO地址空间。PCI配置空间还包括了连入设备的相关信息,根据这些信息,操作系统可以方便地使用相应的驱动来使用这些设备。为了使PCI总线公平地使用PCI总线,提供了一种等待计时的功能,计时器在设备获得了总线使用权时以PCI时钟信号的速率开始计时,直到减为零,设备释放总线占有权。

3、关于PCI的中断

四个中断,属于电平触发方式(边沿触发方式的中断容易丢失)。单功能设备只是使用INTA#,多功能设备使用多个中断。四个中断通过PCI桥(两个PCI总线之间)映射到系统中断上,所以软件无从得知是那个PCI中断。后来的PCI加入了消息信号中断的机制,PCI-Express使用的也是消息信号中断机制,而没有物理中断线。

4、PCI电气规范

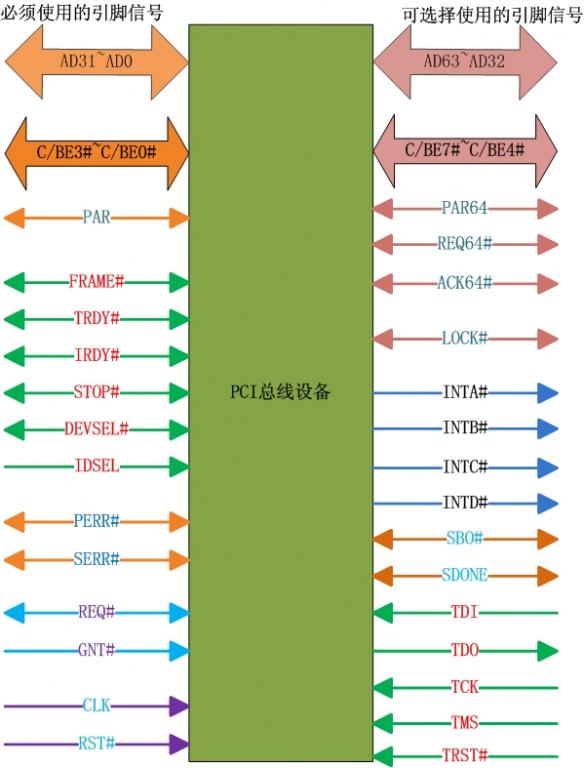

PCI卡的尺寸,长度为174.63mm,高度为36.068~106.68mm。一下是一幅PCI个引脚定义的图。

5、PCI设备的初始化

机器上电的时候,配置软件必须扫描PCI总线,确定有哪些PCI设备,然后加载相应的驱动程序。所有PCI设备都必须实现PCI协议规定必须的配置寄存器。而对PCI配置访问实际上就是访问设备的配置寄存器。

6、PCI配置空间

配置空间各项数据说明:

厂商识别码(Vendor ID):标识设备的制造者,有PCI SIG来分配。0FFFH表示未配置任何设备。

设备识别码(Device ID):标识特定的设备,具体代码由厂商分配。

版本ID,Revision ID:指定一个设备特有的版本号。

Class Code(分类代码):用于设备分类。0BH处为基本分类代码;0A处为子分类代码;09H处为标识一个专用的寄存器级编程接口,便于设备的软件可以与设备交互数据。

命令寄存器(Command):为发出和响应PCI总线命令提供了对设备粗略的控制。

状态寄存器(Status):用于记录PCI总线有关操作的状态信息,系统对该寄存器的读操作无特殊要求。

基地址寄存器(Base Address Registers):供地址映射使用,使PCI的IO映射以及内存映射与具体设备无关。

扩展ROM的基地址寄存器(Expansion ROM Base Address):用来处理那些配置了局部EPROM或者Flash ROM的基地址和大小。Cache大小寄存器:用来指定系统中Cache行的长度,每个参加Cache协议的设备都要使用该寄存器。

延时计时器:该寄存器以PCI总线时钟为单位指定PCI总线主设备的延迟计时器。

内含自测寄存器:可选的寄存器,用作内含自测试的控制与状态寄存器。

中断引脚寄存器(Interrupt Pin):用来表示设备使用了哪个PCI中断引脚。

中断线寄存器(Interrupt Line):用来表示设备中的中断引脚与系统可编程控制器8259的哪个中断输入线相连接。

MAX_GNT表示设备需要多长的突发传输时间。MAX_LAT表示对PCI总线进行访问的频繁程度。

Card CIS Pointer:由在卡总线和PCI之间共享芯片的设备实现。

子系统厂商标识和子系统标识(Subsystem Vendor ID):用于惟一地标识设备所驻留的插入卡和子系统。即插即用操作系统可以定位正确的驱动程序,装载到存储器。

7、PCI扩展ROM

通过执行扩展ROM存放的代码来完成与设备相关的初始化,同时也可能完成系统引导功能。该机制允许扩展ROM中含有几个不同的映像,以适应不同的机器和处理器结构。

凡是支持扩展ROM的设备,必须支持按任意字节组合方式对ROM进行访问,特别强调的是要支持双字(DWORD)访问。扩展ROM中的信息安排要与现有的适合于ISA和EISA以及MC适配器的Intel X86扩展ROM中的头标区兼容。头标区中所给信息经过了扩充,从而使适配器的功能进一步优化使用,从而可以使扩展ROM中的代码在运行期间所使用的存储空间最小。

PCI扩展ROM中代码从不在原地执行,而是将代码从ROM中拷贝到RAM中执行。这样可以在初始化和运行时动态地确定代码长度,并且能够

PCI总线接口技 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)