TWI接口

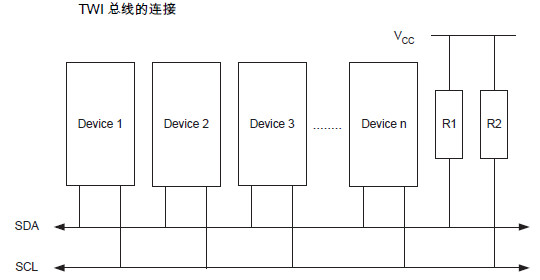

总线的速度有两个不同的规范,一种的速度低于100kHz,而另外一种的速度高达400kHz,总线间的电容不能大于400pF。所有TWI兼容的器件的总线驱动都应该是漏极开路或集电极开路的结构,这样就可以实现线与的功能。TWI器件在输出为0时,TWI总线会产生低电平。当所有的TWI器件输出为三态时,总线会输出高电平,如果接有上拉电阻电压将会被拉高。

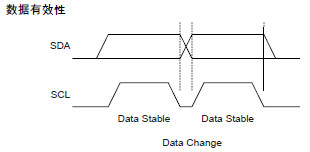

TWI总线上传输的数据是通过在时钟线(SCL)高电平期间对应的数据线(SDA)上的电平来判别的。可通过下图来描述。

在上图中,当SCL拉高期间对应的SDA的电平,如果是高则这位数据就是1,反之则是0。只有在SCL为低电平期间,SDA才可以更新下一位的数据。TWI总线上数据的传送就是通过SCL为高时对应到的SDA的值来构成的。显然,SCL的频率决定了数据传送的速度。

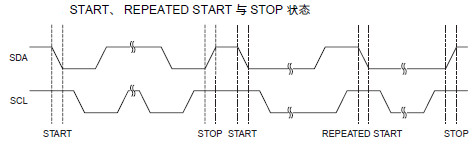

除了传送的数据以外,在每一帧数据传送之前,还会有一个启动信号,以通知从机准备接收数据。在数据传送结束之后,也会有一个停止信号,以通知从机数据传输结束。启动信号是这样来定义的,在SCL为高电平期间,若对应的SDA线上有一个由高变低的电平下跳沿,则表示这是一个启动信号。同样,停止信号是这样定义的,在SCL为高电平期间,若对应的SDA线上有一个由低变高的电平上跳沿,则表示这是一个停止信号。为了形成启动或停止信号,必须在判别该信号的SCL拉高之前做好电平准备,比如要形成一个停止信号,必须在SCL为低电平期间把SDA上的电平拉低,以便在紧跟着后面的SCL高电平期间把SDA的电平拉低,形成一个停止信号。当已经有一个启动信号之后,在没有停止信号出现之前若再次出现启动信号,则表示该信号是一个重新启动信号,它主要用于在主机不放弃总线控制的情况下启动新的传送。上述整个过程可用下图来描述。

通过上述讨论,说明了TWI总线的数据位传送与时钟脉冲是同步的。除了启动与停止状态之外,当时钟线为高电平时,数据线上的电压(不论是高还是低)必须保持稳定,否则有可能被识别成停止信号或重新开始的信号。

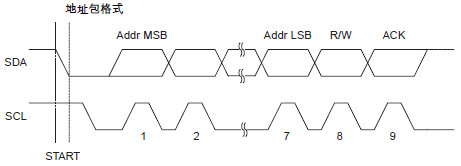

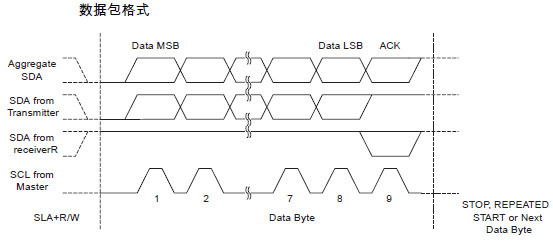

下面来看TWI总线是如何寻址的。在启动信号之后紧接着的就是地址帧,所有的地址包均为9位,包括7位地址位、1位READ/WRITE控制位(即方向位,表明是主机写从机还是从机写主机)与1位应答位。如果READ/WRITE为1,则执行读(从机写主机)操作;否则执行写(主机写从机)操作。从机被寻址后,必须在第九个SCL(ACK)周期通过拉低SDA作出应答。发送地址时先发送高位后发送低位,地址字节的MSB(数据的最高位)先被发送,从机地址由用户自行分配,但要避开保留的广播地址(即地址0000000)。地址的传输格式可用下图来描述。

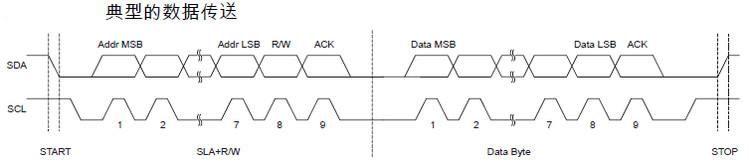

下面来看,如何将地址包和数据包组合为一个完整的传输过程。发送主要由START状态、SLA+R/W、至少一个数据包及STOP状态组成。只有START与STOP状态的空信息是非法的。当主机设定的时钟速度相对于从机太快,或从机需要额外的时间来处理数据时,从机可通过拉低SCL来延长SCL低电平的时间。从机延长SCL低电平的时间不会影响SCL高电平的时间,因为SCL高电平时间是由主机决定的。一个典型的数据传送的过程可用下图来描述。

要注意一点,SLA+R/W与STOP之间传送的字节数由应用程序的协议决定。

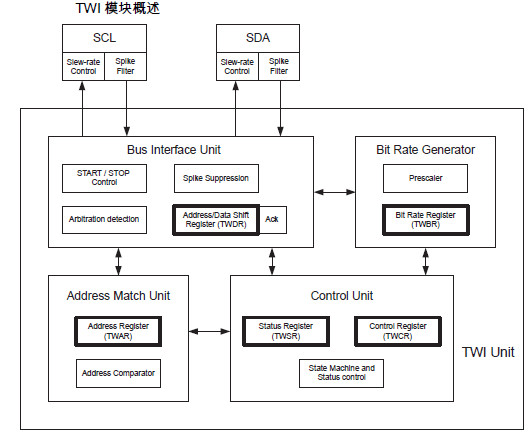

下面来看AVR内部的TWI模块,它是由几个子模块组成,其内部结构图如下。

在上图中,位于粗线之中的寄存器可以通过程序进行访问。SCL与SDA为MCU的TWI接口引脚。引脚的输出驱动器包含一个波形斜率限制器以满足TWI的信号规范。引脚的输入部分包括尖峰抑制单

TWI接口IIC总线接 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)