SPI总线CPOL CPHA

最近在看关于Silicon Labs的C8051F347的某个驱动中,关于SPI部分初始化的代码,看到其对于SPI的设置为CPOL=1,CPHA=0,对于CPOL及CPHA的含义不了解,想要搞懂,这两个参数到底是什么意思,以及为何要这么设置。所以才去找了SPI的极性和相位的相关资料,整理如下。

设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。

SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。

一个master可以接一个或多个slave。

常见用法是一个Master接一个slave,只需要4根线:

SCLK:Serial Clock,(串行)时钟

MISO:Master In Slave Out,主设备输入,从设备输出

MOSI:Master Out

SS:

SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。

而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。

而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

先简单说一下,关于SPI中一些常见的说法:

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity =

(2) CKPHA (Clock Phase)

(3) SCK=SCLK=SPI的时钟

(4) Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)

对于一个时钟周期内,有两个edge,分别称为:

Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

Trailing edge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

本文采用如下用法:

极性=CPOL

相位=CPHA

SCLK=时钟

第一个边沿和第二个边沿

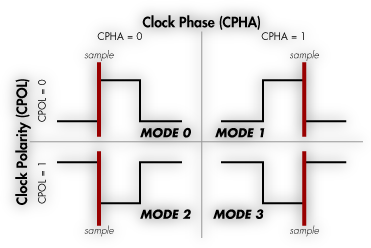

CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:

| Mode 0 | CPOL=0, CPHA=0 |

| Mode 1 | CPOL=0, CPHA=1 |

| Mode 2 | CPOL=1, CPHA=0 |

| Mode 3 | CPOL=1, CPHA=1 |

单独看这张图,的确很难明白具体含义,所以下面会有更详细的解释。

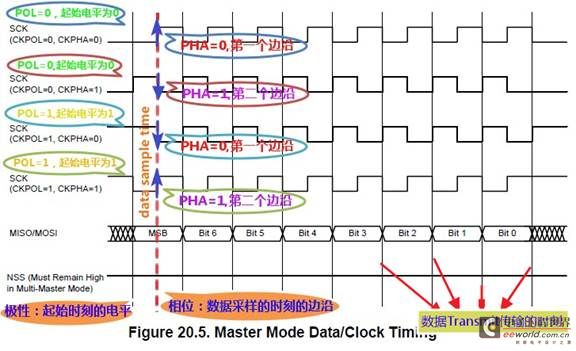

先说什么是SCLK时钟的空闲时刻,其就是当SCLK在数发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

先说英文,其精简解释为:Clock Polarity = IDLE state of SCK。

再用中文详解:

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:

CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;

CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;

首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。

相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

对于:

CPHA=0,表示第一个边沿:

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

CPHA=1,表示第二个边沿:

对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;

用图文形式表示,更加容易看懂:

此处,再多解释一下可能会遇到的CKP和CKE,其是Microchip的PIC系列芯片中的说法。

(1)CKP是Clock Polarity Select,就是极性=CPOL:

CKP,虽然名字和CPOL不一样,但是都是指时钟相位的选择,定义也一样:

CKP: Clock Polarity Select bit

1 = Idle state for clock (CK) is a high level

0 = Idle state for clock (CK) is a low level

所以不多解释。

(2)CKE是Clock Edge Select,就是相位=CPHA:

CKE: SPI Clock Edge Select bit

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on trans

PI总线CPOLCPH 相关文章:

- SPI总线之CPOL CPHA(12-15)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)