- 性位)的最后一位(第8 个位)为显性电平,也不视为格式错误。

- 即使接收单元检测出数据长度码(DLC)中9∼15 的值时,也不视为格式错误。

1.10 错误帧的输出时序

检测到发生错误的单元输出一个错误标志,以通知其它单元。

处于主动错误状态的单元输出的错误标志为主动错误标志;处于被动错误状态的单元输出的错误标志为被动错误标志。

发送单元发送完错误帧之后,将再次发送数据帧或遥控帧。

错误标志输出时序如表9:

1.11 位时序

在没有重新同步情况下,发送单元每秒传输的位数称之为位速率。1位由下面4个段组成。

- 同步段(SS)

- 传播时间段(PTS)

- 相位缓冲段1(PBS1)

- 相位缓冲段2(PBS2)

这些段又由称之为Time Quantum(以下称为Tq)的最小时间单位构成。

1位分为4个段,每个段由若干个Tq构成,这称为位时序。

1位由多少个Tq构成、每个段由多少个Tq构成等是可以设定的。通过设置bit时序。使得可以设定一个采样点以使总线上多个单元可同时采样,所谓采样点就是在这一时刻总线上的电平被锁存,这个锁存的电平作为位的值。采样点的位置在PBS1的结束处。

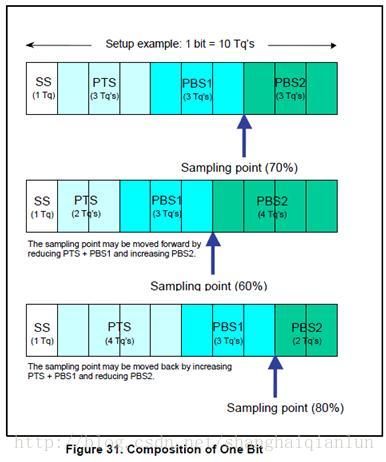

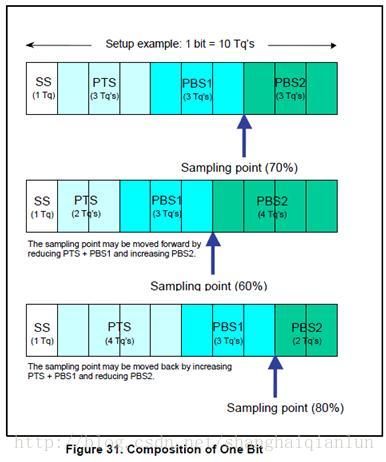

表10描述了各段的作用和Tq 数。1个位的构成如图31所示。

段名称 | 段的作用 | Tq数 |

同步段(SS) | 多个连接在总线上的单元通过此段实现时序的定时调整,以便同步进行接收和发送的工作。 隐性电平到显性电平或显性电平到隐性电平变化的边沿被期望出现在本段。 | 1 | 8-25 |

传播时间段(PTS) | 用于吸收网络上的物理延迟的段。包括发送单元的输出延迟、总线上信号的传播延迟、接收单元的输入延迟。 这个段的时间是以上延迟时间累加和的两倍。 | 1-8 |

相位缓冲段1(PBS1) | 当信号边沿不能出现在SS 段时,此段用来矫正误差。 由于各单元以各自独立的时钟来工作,细微的时钟误差都会累积起来,PBS 段可用于吸收此误差。 为了吸收一个时钟误差,在SJW设置的范围内增减PBS1和PBS2,PBS1和PBS2越大,允许误差越大,但是通讯速度会降低。 | 1-8 |

相位缓冲段2(PBS2) | PBS1或IPT中较大者(见注1和2) |

重新同步跳转宽度(SJW) | 因时钟频率偏差、传送延迟等原因,某些单元可能会失去同步。SJW是所能校正的最大失去同步的宽度。 | 1-4*PBS1 |

注1:IPT代表信息处理时间,是以采样点作为起始的时间段,用于计算后续位的位电平。这是硬件在一个采样点后立刻改变位的电平所必须要的。这个时间等于或小于2Tq,。

注2:因为采样点是处于PBS1结束处,所以IPT和PBS2重叠。当IPT = 2Tq时,PBS2不可能选为1,因此,PBS2必须是2到8Tq。

注3:重新同步的结果使相位缓冲段1增长,或使相位缓冲段2 缩短。相位缓冲段加长或缩短的数量有一个上限,此上限由SJW(重新同步跳转宽度)给定。重新同步跳转宽度应设置于1和最小值之间(此最小值为4*PBS1)。

可以从一位值转换到另一位值的过渡过程得到时钟信息。这里有一个属性,即:只有后续位的一固定最大数值才具有相同的数值。这个属性使总线单元在帧期间重新同步于位流成为可能。可用于重新同步的两个过渡过程之间的最大的长度为29个位时间。

1.12 同步是如何获得的?

CAN总线的通讯是采用NRZ(Non-Return to Zero,非归0)码,数据本身并不携带时钟信息,也即在每一位的开始或结束没有同步信号,发送单元以位时序同步的方式开始发送帧数据,接收单元根据总线电平的变化进行同步并进行接收工作。

然而,发送器和接收器之间由于彼此的时钟误差或传输路径的相位误差可能会失去同步关系,因此接收单元在接收帧的时候,必须通过硬件同步或重新同步调整它的操作时序。

1.13 硬件同步

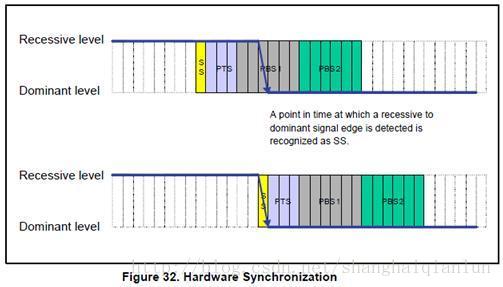

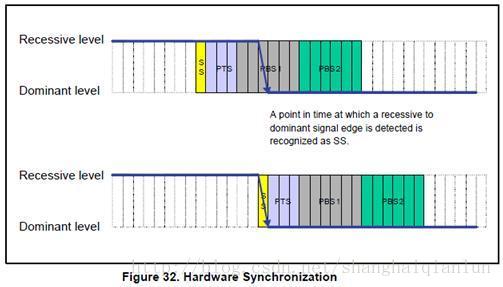

在总线空闲状态时,接收单元检测到SOF,就会执行这个同步调整过程。“隐式”电平跳变到“显式”电平的边缘的时间点被认为是SS,而不管SJW的值

图32显示了硬件同步机制。

- 如果沿出现在SS里,沿的相位误差e=0;

- 如果沿位于采集点(PBS1结束之前)之前,e>0;

- 如果沿位于采集点之后,e<0;

1.14 重新同步机制

在接收过程中检测到总线电平发生了改变时执行重新同步操作。

每当检测到一个边沿(总线电平的改变),收发单元根据SJW值通过增加PBS1段或减少PBS2段,来调整同步。但,如果发生了超出SJW值的误差时,最大调整量不能超过SJW值。

图33显示了重新同步机制。

1.15 调整同步的规则

硬件同步和再同步的执行遵从如下规则:

1) 在1个位时间里(或者说在2个采样点之间),只允许一个同步(或者说只进行一次同步调整)。

2) 只有当采样点之前的总线电平和边沿后的总线电平不同时,该边沿才能用于调整同步。

3) 如果出现隐性电平到显性电平变化的边沿,且条件(1)和(2)满足,将进行同步。

4) 如果在帧间间隙期间发生隐性电平到显性电平的信号边沿(除了间隙里的第一位),则总会执行硬件同步。