设计高速PCB应注意的电源完整性问题以及地弹噪声

并不能解决所有的问题。首先,你不能将所有的关键器件放在电路板的中心。通常情况下,器件放置的灵活性是有限的。其次,在任何给定的位置总有一些谐振模式会被激发。例如,图3中绿色曲线表示当你将芯片放置在沿某一坐标轴偏移中心位置时, 0.54GHz的谐振模式将被激发。成功的设计电路板的PDS(电源分配系统)的关键在于在合适的位置增加退耦电容,以保证电源的完整性和在足够宽的频率范围内保证地弹噪声足够校

退耦电容

设想FPGA在0.2纳秒的上升沿吸入2A的电流,此时电源电压会暂时降低(压降),而地平面电压会暂时被拉高(地弹)。其变化幅度取决于电路板的阻抗和芯片偏置管脚处的用于提供电流的退耦电容。

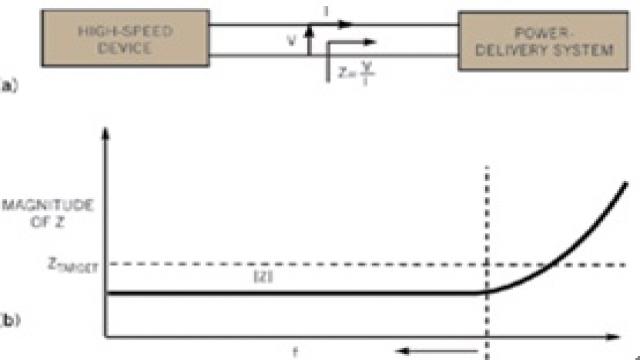

由于电流的瞬变值为2A,电压的瞬变值由V=Z×I决定,Z是从芯片端看出的阻抗,因此,为了避免电压的尖峰波动,在从直流到信号带宽的频率范围内,Z值必须低于某一门限值。

图4,其变化幅度取决于电路板的阻抗和芯片偏置管脚处的用于提供电流的退耦电容;为了避免电压的尖峰波动,在从直流到信号带宽的频率范围内,Z值必须低于某一门限值。图中虚线部分即为PDS阻抗应该满足的目标区域。

在该设计中,为了保持电源完整性,电源—地的电压波动必须保持在标准值3.3V的5%以内。因此噪声不能大于0.05×3.3V=165 mV。可以据此按照欧姆定律计算出PDS的最大阻抗165mV/2A=82.5mΩ,图4中虚线部分即为PDS阻抗应该满足的目标区域。

对于最低频率,通常是1kHz或者更低的频率——电源满足阻抗特性的要求,电源和地层的结构通常不会破坏阻抗特性,因为它们呈现低电阻与电感特性。而当频率高于1kHz时,电流通路的互感大到足以使电压超过限定值,根据:

V=L*(di/dt)

对于更高的频率,退耦电容作为电源层与地层之间的低阻抗连接是必要的。需要满足PDS阻抗要求的信号带宽可由下式估计:

F(GHz)=0.35/TTRANSITION(nSEC)

在该设计中,其带宽为1.75GHz。为了达到这么宽的带宽,通常需要在MHz信号区域放置很多高频瓷片电容,在kHz信号区域放置体积较大的电解电容。这些电容矩阵与其它器件共同占用宝贵的电路板空间。在反复试验的设计方法中,物理原型是不可缺少的,而虚拟原型技术使设计者可以在不需要物理原型的基础上解决这个问题。

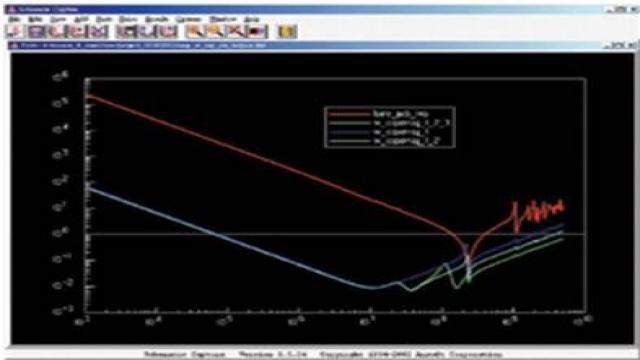

为PCB板设计PDS,例如此例中的xDSM板,使用SIwave可以在IC芯片处放置一个端口,计算电路板在适当带宽内的输入阻抗。图5中红色曲线显示的是电路板上无电容时的阻抗。阻抗轴与频率轴都取对数坐标。仿真显示了电路板本身电容的影响而忽略了经过电源的低感应电流回路。从图中可以看出,阻抗随着频率的减少而增加,但由于经过电源的回路也有低阻抗,因此这种关系并不是严格的。

图5,红色曲线显示的是电路板上无电容时的阻抗;深蓝色曲线是经过重新设计后的阻抗特性;浅蓝色曲线是又增加10nF电容矩阵后的阻抗曲线;绿色曲线表示再次增加1nF电容矩阵后的结果。

根据Z=1/(j·C),红色曲线中的直线部分表明电路板本身的电容为74nF。为了使阻抗在1MHz处低于目标阻抗82.5mΩ,电容值至少应为 2μF——几乎是电路板本身电容的30倍。为此首先需要增加22个0.1μF的电容矩阵。图中深蓝色曲线是经过重新设计后的阻抗特性。在大多数的频率范围内,设计满足了阻抗特性的要求。但在带宽的高端,电容的ESL(等效串联电感)、ESR(等效串联电阻)以及由电容间距带来的附加电感使阻抗曲线没有达到阻抗特性要求。

由于更小的电容具有更小的ESL和ESR值,因此增加旁路有助于提高其高频特性。图5中的浅蓝色曲线是又增加10nF电容矩阵后的阻抗曲线。绿色曲线表示再次增加1nF电容矩阵后的结果。每一级别电容矩阵的增加都提高了阻抗特性,但结果仍然刚刚满足阻抗特性的要求。

在设计的这个阶段,设计者可以增加电磁仿真与电路仿真一起来完成设计。这种方法使设计者可以精确地为低端的阻抗建模,包括电源的负载效应

- 高速信号线走线规则(08-08)

- 高速PCB设计中的EMI设计要点和规则(03-30)

- 传输线对数字信号的影响(04-26)

- 基于赛灵思Virtex-5 FPGA实现LTE仿真器(04-29)

- MF-TDMA卫星通信网络仿真测试研究(04-11)

- 各大仿真软件介绍(包括算法,原理)(09-08)