DS90CF364 LVDS发送/接收器在RGB液晶屏应用

线-FPLINE(HSYNC)、FPFRAME(VSYNC)和DRDY(Data Enable)。;

RxIN+:LVDS差分数据输入的正端;

RxIN-:LVDS差分数据输入的负端;

RxCLK OUT:TTL电平时钟输出,通常在其下降沿激活数据;

RxCLK IN+:LVDS差分时钟输入正端;

RxCLK IN-:LVDS差分时钟输入负端;

PWR DWN:TTL电平输入,当设置为低时,输出为三态,以便确保在节能状态下的低电流;

Vcc:用于TTL的电源引脚;

GND:用于TTL的电源地;

PLL Vcc:用于PLL的电源引脚;

PLL GND:用于PLL的电源地;

LVDS Vcc:用于LVDS输出的电源引脚;

LVDS GND:用于LVDS输出的电源地。

4 设计应用

本文所介绍的系统板设计并不是太难,但需注意以下两点:

(1)PCB板设计

最好使用4层板,从顶层到底层的顺序依次为LVDS信号层、地层、电源层、TFL信号层,这样可使TIL信号和LVDS信号相互隔离,否则T1L可能会耦合到LVDS线上,鉴于上述原因,设计时最好将TIL和LVDS信号放在由电源/地层隔离的不同层上。安装时,LVDS发送器和接收器应尽可能地靠近连接器的LVDS端。使用分布式的多个电容来旁路LVDS设备时,表面贴电容应尽量靠近电源/地层管脚放置,以进行更好地滤波和防止电源干扰。电源层和地层应尽量布一些粗线,以保持PCB地线层返回路径宽且短,应该利用地层返回铜线的电缆连接两个系统的地层,可使用多过孔(至少两个)将其连接到电源层(线)和地层(线),表面贴电容可以直接焊接到过孔焊盘以减少线头。所有未使用的LVDS接收器输入管脚均应悬空,同时所有未使用的LVDS和TIL输出脚也应悬空,并将未使用的TIL发送/驱动器输入和控制/使能管脚接到电源或地端。

(2)电缆选择

使用受控阻抗媒质时,其差分阻抗约为100Ω,因而不会引入较大的阻抗不连续性,但就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)通常比非平衡电缆好。电缆长度小于0.5m时,大部分电缆都能有效工作,距离在0.5-10m之间时,CAT 3(Categiory 3)双绞线对电缆的效果较好,因此,在距离大于10m并且要求高速率时,建议使用CAT 5双绞线对。如需在噪声环境中提高可靠性,最好选用带屏蔽层的电缆,每对电缆之间一定要靠紧,并且应在尽量靠近接收器的每对平行线正端和负端之间连接一个100Ω的表面贴终端电阻,该电阻可在设计时起到终止环流信号的作用。另外在接收端串接一个变压器可以减小干扰并避免LVDS驱动器和接收器地电位差所产生的影响。

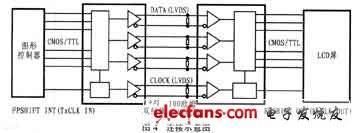

该芯片组的应用连接示意图如图4所示,设计时可参照该图进行。

5 结束语

本文介绍的LVDS传输套片还可运用于其它具有数字RGB视频接口的控制芯片。对于美国国家半导体公司出品的其它FPD链路专用LVDS传输套片,也可借鉴本文所介绍的方法来进行设计和调试。

DS90CF364LVDSRGB接口液晶 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)